Процесори Intel - як влаштовані і основні принципи. Процесор. Типи і відмінності процесорів

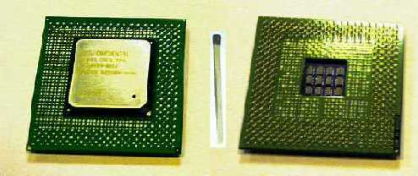

Етапи розвитку МП, відповідні досягнення, їх основні архітектурні та інші характеристики природно розглянути на основі МП фірми Intel (INTegrated ELectronics). Є також ряд фірм - AMD (Advanced Micro Devices), Cyrix, Texas Instruments і ін., Які своїми виробами більш-менш успішно конкурують з корпорацією Intel.

Основні параметри МП наступні:

- тактова частота;

- ступінь інтеграції мікросхеми (скільки транзисторів міститься в чіпі);

- внутрішня розрядність даних (кількість біт, які МП може обробляти одночасно);

- зовнішня розрядність даних (кількість одночасно переданих біт в процесі обміну даними ЦП з іншими елементами);

- адресуемая пам'ять (залежить від числа адресних біт).

Процесори Intel

(22 березня 1993 г.). Pentium є  суперскалярний процесор з 32-бітової адресною шиною і 64-бітової шиною даних, виготовлений по субмикронной технології з компліментарної МОП-структурою складається з 3,1 млн транзисторів (на площі 16,25 см2). Процесор включає наступні блоки:

суперскалярний процесор з 32-бітової адресною шиною і 64-бітової шиною даних, виготовлений по субмикронной технології з компліментарної МОП-структурою складається з 3,1 млн транзисторів (на площі 16,25 см2). Процесор включає наступні блоки:

- Ядро (Core). Основне виконавчий пристрій. Продуктивність МП при тактовій частоті 66 МГц становить близько 112 млн команд в секунду (MIPS). У порівнянні з процесором 80486 DX було досягнуто 5-кратне збільшення продуктивності завдяки двом конвеєрів, що дозволяє виконати одночасно кілька команд.

- Провісник переходів (Branch Predictor) намагається вгадати напрямок розгалуження програми і заздалегідь завантажити інформацію в блоки передвибірки і декодування команд.

- Буфер адреси переходів (Branch Target Buffer BTB) забезпечує динамічний пророцтво переходів. Принцип дії: «Якщо передбачення вірно, то ефективність збільшується, а якщо немає, то конвеєр доводиться скидати повністю». Згідно з даними Intel, ймовірність правильного передбачення переходів в процесорах Pentium становить 75-80%.

- Блок плаваючою точки (Floating Point Unit) виконує обробку чисел з плаваючою точкою. Обробка графічної інформації, мультимедіа-додатків і інтенсивне використання ПК для вирішення обчислювальних завдань вимагають високої продуктивності при виконанні операцій з плаваючою крапкою.

- Кеш-пам'ять 1-го рівня (Level I cache). Процесор має два банки пам'яті по 8 Кбайт, 1-й - для команд, 2-й - для даних, які мають більшу швидкодію, ніж більш ємна зовнішня пам'ять кеш-пам'ять (L2 cache)

- Інтерфейс шини (Bus Interface). Передає в ЦП потік команд і даних, а також передає дані з ЦП.

У процесорі Pentium введений режим управління системою SMM (System Management Mode). Цей режим дає можливість реалізовувати системні функції дуже високого рівня, включаючи управління живленням або захист, прозорі для ОС і виконуються додатків.

Перехід на тактову частоту 60 МГц і вище був значним досягненням, і були відповідним чином вирішені проблеми охолодження (поверхню процесора при цьому нагрівається до 85 ° С).

(1 листопада 1995 г.). В Pentium Pro для підвищення продуктивності була застосована буферна пам'ять (кеш) другого рівня ємністю 256 Кбайт, розташована в окремому чіпі і змонтована в корпусі ЦП. В результаті стала можливою ефективна розвантаження п'яти виконавчих пристроїв: два блоки цілочисельний арифметики; блок завантаження; блок запису; FPU (Floating-Point Unit - пристрій арифметичних операцій з плаваючою точкою).

Pentium P55 (Pentium MMX)8 січня 1997 р Pentium MMX - версія Pentium з додатковими можливостями. Технологія ММХ повинна була додати / розширити мультимедіа можливості комп'ютерів. Реалізована методика SIMD (ОКМД), орієнтована на алгоритми і типи даних, характерні для програмного забезпечення мультимедіа. ММХ оголошений в січні 1997 року, тактова частота 166 і 200 МГц, в червні того ж року з'явилася версія 233 МГц. Технологічний процес 0,35 мкм, 4,5 млн транзисторів.

(7 травня 1997 г.). Процесор являє собою модифікацію Pentium Pro з підтримкою можливостей ММХ. Перші PII оголошені як процесори для настільних високопродуктивних (high-end) комп'ютерів. Була змінена конструкція корпусу - кремнієву пластину з контактами замінили на картридж, збільшена частота шини і тактова частота, розширені ММХ-команди.

Є також модель для ноутбуків - Pentium II РЕ і для робочих станцій - Pentium II Хеоn 450 МГц.

Celeron (15 квітня 1998 г.). Celeron - спрощений варіант Р2 для дешевих комп'ютерів. Основні відмінності цих процесорів в обсязі кеша другого рівня частоті шини. Всі ці процесори виконані по 0,25 мкм технології і мають від 7,5 до 19 млн транзисторів.

(26 лютого 1999 г.). Р3 - один з найбільш продуктивних процесорів Intel, але в своїй конструкції він мало чим відрізняється від Р2, збільшена частота та додано близько 70 нових команд. У жовтні 1999 р також випущена версія для мобільних комп'ютерів, виконана по 0,18 мкм технології з частотами від 400 до 733 МГц. Для робочих станцій і серверів існує РЗ Хеоn, орієнтований на системну логіку GX з об'ємом кеша другого рівня 512 Кбайт, 1 або 2 Мбайт. Технологічний процес 0,25 мкм, системна шина працює на частоті 100 МГц, є 0,18 мкм версія з частотою шини 133 МГц, а також моделі на 600, 666 і 733 МГц.

(Willamette, 2000 р .; Northwood, 2002 г.). Природно, рано чи пізно архітектура РIII повинна була застаріти. Справа в тому, що досягнувши частоти в 1 ГГц, Intel зіткнулася з проблемами в подальшому нарощуванні частоти своїх процесорів: Pentium III на 1.13 ГГц довелося відкликати у зв'язку з його нестабільністю. Подальше нарощування частоти існуючих процесорів приводить все до меншого зростання їх продуктивності. Проблема в тому, що латентності (затримки), що виникають при зверненні до тих чи інших вузлів процесора, в Р6 вже занадто великі.

Таким чином з'явився Pentium IV - в його основі лежить архітектура, названа Intel NetBurst architecture. Цією назвою Intel хотіла підкреслити, що основна мета нового процесора - прискорити виконання завдань потокової обробки даних, безпосередньо пов'язаних з бурхливим розвитком Internet і мультимедіа технологіями.

Архітектура NetBurst має у своїй основі декілька інновацій, в комплексі дозволяють домогтися кінцевої мети - забезпечити запас швидкодії і майбутню наращиваемость для процесорів сімейства Pentium IV. У число основних технологій входять:

- Hyper Pipelined Technology - конвеєр Pentium IV включає 20 стадій;

- Advanced Dynamic Execution - покращене пророкування переходів і виконання команд зі зміною порядку їх слідування (out of order execution);

- Trace Cache - для кешування декодувати команд в Pentium IV використовується спеціальний кеш;

- Rapid Execute Engine - ALU процесора Pentium IV працює на частоті, удвічі більшою, ніж сам процесор;

- SSE2 - розширений набір команд для обробки потокових даних;

- 400 МГц System Bus - нова системна шина.

Pentium IV Prescott (Лютий 2004 року). На початку лютого 2004 р Intel анонсувала чотири нові процесори Pentium IV (2,8; 3,0; 3,2 і 3,4 ГГц), заснованих на ядрі Prescott, яке включає ряд нововведень. Разом з випуском чотирьох нових процесорів Intel представила процесор Pentium IV 3.4 ЇЇ (Extreme Edition), заснований на ядрі Northwood і має 2 Мбайт кеш-пам'яті третього рівня, а також спрощену версію Pentium IV 2.8 А, засновану на ядрі Prescott з обмеженою частотою шини ( 533 МГц).

Нові процесори мають таку ж конструкцію, що і засновані на ядрі Northwood, тому для їх відмінності Intel ввела новий індекс в назві процесора - Є. Наприклад, процесор Pentium IV 3.2 З заснований на ядрі Northwood, має підтримку 800 МГц шини і технології НТ, в той час як Pentium IV 3.2 Е виконаний на ядрі Prescott і також підтримує 800 МГц шину і технологію НТ.

Prescott виконаний за технологією 90 нм, що дозволило зменшити площу самого кристала, при цьому загальне число транзисторів було збільшено більш ніж в 2 рази. У той час як ядро Northwood має площу 145 мм 2 і на ньому розміщено 55 млн транзисторів, ядро Prescott має площу 122 мм 2 і містить 125 млн транзисторів.

Процесори Cyrix

Оприлюднений в жовтні 1995 року, 6x86 був  першим сумісним з Pentium процесором, що дозволяв проникнути на ринок і домогтися співпраці з IBM Microelectronics Division. Ухвалення 6x86 було спочатку повільним, тому що Cyrix встановив занадто високі ціни, помилково думаючи, що, так як ефективність процесора була порівнянна з Intel, його ціна могла бути такою ж. Як тільки Cyrix переглянув свої позиції, чіп став чинити значний вплив в частці відповідного сектора ринку як високоефективна альтернатива серії Pentium.

першим сумісним з Pentium процесором, що дозволяв проникнути на ринок і домогтися співпраці з IBM Microelectronics Division. Ухвалення 6x86 було спочатку повільним, тому що Cyrix встановив занадто високі ціни, помилково думаючи, що, так як ефективність процесора була порівнянна з Intel, його ціна могла бути такою ж. Як тільки Cyrix переглянув свої позиції, чіп став чинити значний вплив в частці відповідного сектора ринку як високоефективна альтернатива серії Pentium.

Починаючи з 6x86, процесори Cyrix були здатні до рівня продуктивності, еквівалентному чіпу Pentium, але при більш низькій частоті. Для оцінки продуктивності використовується Processor Performance Rating - Р-рейтинг (позначення Р100 +, наприклад, символізує продуктивність, еквівалентну Pentium з частотою 100 МГц). Процесори Cyrix (як і AMD) традиційно працюють на більш низьких частотах, ніж чисельне значення їх Р-рейтингу, без помітного зниження продуктивності. Наприклад, Р133 + (Р-рейтинг) працює на частоті 110 МГц, в той час як Р150 + і Р166 + працюють на 120 і 133 МГц відповідно.

Перевага 6x86 випливало з удосконалень архітектури чіпа, яка дозволила 6x86 отримувати доступ до її внутрішнього кешу і регістрів в одному циклі частоти (Pentium зазвичай задіює два або більше циклів для доступу до кешу). Крім того, первинний кеш 6х86-го був об'єднаний, замість того, щоб включити дві окремі секції 8 Кбайт для команд і даних. Ця об'єднана модель була в стані зберігати команди і дані в будь-якому відношенні, забезпечуючи «ймовірність попадання» кеша в межах 90%. ЦП містить 3,5 млн транзисторів, спочатку виготовлених за технологією п'яти 0,5-мікронних шарів. Інтерфейс - Socket 7. Напруга живлення ядра - 3,3 В. Характеристики 6x86 подібні Pentium. Однак він включає і нові характеристики: видалення залежності даних, пророкування переходів, виконання команд поза природного порядку (можливість більш швидких команд виходити з черги конвеєра, не порушуючи процес виконання програми). Все це підвищує рівень продуктивності 6x86, на відміну від Pentium з такою ж частотою.

Однак процесори 6x86 стикалися з безліччю проблем, особливо перегрівом, низькою продуктивністю при роботі з плаваючою комою і несумісністю з Windows NT. Це несприятливо впливало на успіх процесора, і конкуренція з Pentium виявилася недовгою і закінчилася з запуском Intel Pentium ММХ.

Cyrix MediaGX. Введення процесора MediaGX в лютому 1997 р визначило першу нову архітектуру PC в десятилітті і визначило новий сегмент ринку - дешевий «Основний ПК». Зростання цього ринку був бурхливим, і технологія процесора Cyrix і нововведення рівня системи були ключовим елементом.

Чим більше процесів, які обробляються на центральному процесорі ПК безпосередньо, тим вище загальна продуктивність системи. У традиційних комп'ютерних технологіях центральний процесор обробляє дані на частоті в мегагерци, в той час як шина, яка переміщує дані в (і від) інші компоненти, працює тільки на половинній швидкості або навіть менше. Це означає, що рух даних до (і від) центрального процесора може тривати довше. Cyrix усунув це вузьке місце введенням технологією MediaGX. Архітектура MediaGX об'єднує графічні та звукові функції, інтерфейс PCI і диспетчера пам'яті в блок процесора, таким чином усуваючи потенційні конфлікти системи і проблеми конфігурації кінцевого користувача. Вона складається з двох чіпів - процесора MediaGX і співпроцесора MediaGX Cx5510. Процесор використовує особливу гніздо, яке потребує спеціально розробленої материнської плати. MediaGX - х86-сумісний процесор, який безпосередньо з'єднує на шині PCI і пам'ять EDO DRAM по виділеній 64-бітової шини даних. Cyrix стверджує, що техніка стиснення для використання на шині даних, усуває потребу в кеші другого рівня. Є об'єднаний (16 Кбайт) кеш першого рівня на центральний процесор - того ж обсягу, що і на стандартному чіпі Pentium. Графіка обробляється спеціальним конвеєром на центральному процесорі безпосередньо, і контролер монітора знаходиться також на головному процесорі. Немає ніякої відеопам'яті, буфера кадрів, що зберігаються в головній пам'яті (традиційна Unified Memory Architecture - UMA), замість цього використовується власна Cyrix Display Compression Technology (DCT). Операції з даними VGA виконуються апаратними засобами ЕОМ, але регістри VGA управляються програмами Cyrix - Virtual System Architecture (VSA). Супутній чіп MediaGX Cx5510 містить аудіоконтроллер і також використовує програми VSA, щоб емулювати можливості стандартних звукових карт. Цей чіп з'єднує процесор MediaGX через шину PCI з шиною ISA, а також з IDE і портами введення-виведення, т. Е. Виконує традиційні функції чіпсета.

Відповіддю Cyrix на технологію Intel MMX був 6х86МХ, запущений в середині 1997 року, незадовго до того, як компанія була придбана компанією National Semiconductor. Компанія залишилася вірною формату Socket 7 для свого нового чіпа, це підтримувало на потрібному рівні витрати виробників системи і в кінцевому рахунку споживачів, продовжуючи життя існуючого чіпа і системних плат.

Архітектура нового чіпа залишалася по суті тієї ж самої, як і у його попередника, з доповненням команд ММХ, деякими поліпшеннями до Floating Point Unit, великим (64 Кбайт) універсальним кешем першого рівня і розширеним блоком управління пам'яттю.

Процесор 6х86МХ був добре прийнятий на ринку, оскільки 6х86MX / PR233 (працює на частоті 187 МГц) виявився швидшим, ніж Pentium II (233 МГц) і AMD Кб. MX був також першим провідним процесором, здатним до роботи на зовнішній шині 75 МГц, що забезпечувало очевидні переваги смуги пропускання і підвищувало загальну продуктивність. Однак 6х86МХ працював з плаваючою комою набагато гірше конкурентів, що негативно позначалося на обробці тривимірної графіки.

Cyrix MII. Процесор МII - розвиток 6х86МХ, що працює на більш високих частотах. До літа 1998 р 0,25-мікронних процесори МII-300 і МII-333 проводилися на нових виробничих потужностях компанії National Semiconductor в шт. Мен, націлених на розвиток технології 0,22-мкм, просуваючись до своєї кінцевої мети - 0,18 мкм в 1999 р

Процесори AMD

Тривалий час Advanced Micro Devices,  подібно Cyrix, виробляв центральні процесори 286, 386 і 486, які були засновані на розробках Intel. K5 був першим незалежно створеним х86 процесором, на який AMD покладав великі надії. Однак, покупка компанією AMD заснованого в Каліфорнії конкурента навесні 1996, здається, створила можливість краще підготуватися до своєї наступній атаці на Intel. К6 почав життя як Nx686, будучи перейменованим після придбання NextGen. Серія ММХ-сумісних процесорів КБ була запущена в середині 1997 року, за кілька тижнів до Cyrix 6x86MX, і відразу була схвалена критиками.

подібно Cyrix, виробляв центральні процесори 286, 386 і 486, які були засновані на розробках Intel. K5 був першим незалежно створеним х86 процесором, на який AMD покладав великі надії. Однак, покупка компанією AMD заснованого в Каліфорнії конкурента навесні 1996, здається, створила можливість краще підготуватися до своєї наступній атаці на Intel. К6 почав життя як Nx686, будучи перейменованим після придбання NextGen. Серія ММХ-сумісних процесорів КБ була запущена в середині 1997 року, за кілька тижнів до Cyrix 6x86MX, і відразу була схвалена критиками.

К6 був майже на 20% менше, ніж Pentium Pro і при цьому містив на 3,3 млн транзисторів більше (8,8 проти 5,5 млн). ЦП К6 підтримував технологію MMX Intel, включаючи 57 нових х86 команд, розроблених для розвитку мультимедійного програмного забезпечення. Рівень продуктивності K6 дуже схожий з Pentium Pro відповідних частот з його максимальним 512 Кбайт кешем другого рівня. Спільне з чіпом Cyrix MX (але в дещо меншій мірі) - робота з плаваючою комою - була областю відносної слабкості в порівнянні з Pentium Pro або Pentium II.

AMD K6-2. Процесори AMD K6-2 з 9,3 млн транзисторів проводилися по 0,25-мікронної технології AMD. Процесор був упакований в 100 МГц Super7 - сумісну, 321-контактну керамічну плату (ceramic pin grid array (CPGA) package). K6-2 включає інноваційну ефективну мікроархітектуру R1SC86, великий (64 Кбайт) кеш першого рівня (двухпортовий кеш даних на 32 Кбайт, кеш команд на 32 Кбайт з додатковим предрасшіфровиваюшім кешем на 20 Кбайт), а також покращений модуль роботи з плаваючою комою.

Ефективна продуктивність при його запуску в середину 1998 року була оцінена в 300 МГц, до початку 1999 р найшвидшим з доступних процесорів була версія 450 МГц. Тривимірні можливості ДО6-2 представляли інше важливе досягнення. Вони були втілені в AMD технології 3DNow !, як новий набір з 21 команди, який доповнював стандартні команди ММХ, вже включені в архітектуру КБ, що прискорювало обробку тривимірних додатків. Анонсований на початку 2001 р процесор ДО6-2 (550 МГц) повинен був стати найшвидшим і заключним процесором AMD для застарілого форм-фактора Socket 7, згодом замінним в перспективному секторі ринку настільних комп'ютерів процесором Duron.

AMD K6-III. У лютому 1999 р AMD оголосила про початок випуску партії 400 МГц AMD K6-III процесора, під кодовою назвою narptooth і випробувала 450 МГц версію. Ключовою особливістю цього нового процесора була інноваційна розробка - Трирівневий кеш.

Традиційно процесори ПК використовували два рівня кешу:

- кеш першого рівня (L1), який зазвичай розташований на кристалі;

- кеш другого рівня (L2), який міг розташовуватися або поза ЦП, на материнській платі або слоті, або безпосередньо на чіпі ЦП.

Загальна емпіричне правило при проектуванні підсистеми кеша - чим більше і швидше кеш, тим вища продуктивність (ядро центрального процесора може швидше отримати доступ до інструкцій і даних).

Визнаючи вигоди великого і швидкого кеша в задоволенні потреб додатків, все більш вимогливих до продуктивності ПК, «Трирівневий кеш» компанії AMD вводив архітектурні нововведення кешу, розроблені для збільшення продуктивності ПК на основі платформи Super7:

- внутрішній K2-кеш (256 Кбайт), що працює на повній швидкості процесора AMD-K6-III і доповнює кеш L1 (64 Кбайт), який був стандартний для всього сімейства процесорів AMD-K6;

- багатопортовий внутрішній кеш, що дозволяє одночасне 64-бітове читання і запис як кешу L1, так і L2;

- первинна процесорна шина (100 МГц), що забезпечує з'єднання з резидентної кеш-пам'яті на системній платі, що розширюється від 512 до 2048 Кбайт.

Проект многопортового внутрішнього кеша процесора AMD-K6-III дозволив як кешу L1 (64 Кбайт), так і кешу L2 (256 Кбайт) виконувати одночасне 64-бітове читання і запис операцій за один такт процесора. На додаток до цього Багатопортовий проекту кеша ядро процесора AMD-K6-III було в змозі отримати доступ до кешах L1 і L2 одночасно, що збільшує загальну пропускну здатність центрального процесора.

AMD стверджувала, що з повністю налаштованим кешем 3-го рівня K6-III мав перевагу в розмірі кешу в 435% перед Pentium III і, отже, суттєва перевага в продуктивності. Однак, в кінцевому рахунку, йому судилося прожити щодо коротке життя на арені настільних комп'ютерів, будучи відсунута на задній план більш ефективним процесором AMD Athlon через кілька місяців.

Випуск процесора Athlon влітку 1999 р був найбільш вдалим ходом AMD. Це дозволило їм пишатися тим, що вони справили  перший процесор сьомого покоління (у нього було досить багато радикальних архітектурних відмінностей від Pentium II / III і K6-III, щоб заслужити назву процесора наступного покоління), і це означало також, що вони вирвали технологічне лідерство у Intel.

перший процесор сьомого покоління (у нього було досить багато радикальних архітектурних відмінностей від Pentium II / III і K6-III, щоб заслужити назву процесора наступного покоління), і це означало також, що вони вирвали технологічне лідерство у Intel.

Давньогрецьке слово Athlon означає «трофей», або «гри». Athlon - процесор, за допомогою якого AMD сподівалася збільшити реальне конкурентоспроможне присутність в корпоративному секторі, крім його традиційного переваги на споживчому ринку і ринку тривимірних ігор. Ядро розміщується на кристалі в 102 мм 2 і містить приблизно 22 млн транзисторів.

Duron. У середині 2000 був випущений процесор Duron, призначений для дому та офісу. Назва походить від латинського «durare» - «вічний», «тривалий». Кеш-пам'ять L1 (128 Кбайт) і L2 (64 Кбайт) розміщується на платі. Первинна системна шина працює на частоті 200 МГц. Підтримується поліпшена технологія 3DNow! Технологія 0,18 мкм, частоти 600, 650 і 700 МГц. Інтерфейс - 462-контактний роз'єм Socket A.

Athlon 64. Восени 2003 р вийшли дві  моделі процесора AMD - Athlon 64 для масового ринку і Athlon 64 FX-51 для мультимедіа і професійних додатків (архітектура К8). В системі позначень AMD Athlon 64 має еквівалентну частоту 3200, при фізичної частоті 2 ГГц, FX-51 трохи більше - 2,2 ГГц. Важливе архітектурне нововведення: інтеграція системного контролера пам'яті (system memory controller hub - MCH) безпосередньо в процесор. Це означає, що системна плата (точніше, чіпсет) не повинна більше утримувати окремий чіп контролера Northbridge. Крім того, зникає необхідність в первинної системної шини (FSB) разом з усіма змінами, що вносяться нею затримками. Замість цього К8 використовує HyperTransport (системна шина пропускною спроможністю до 6,4 Гбайт / с) для з'єднання з контролерами Southbridge, AGP або іншими ЦП. Це дозволяє пам'яті працювати з повною частотою процесора, знижує затримки (латентність) і підвищує ефективність пам'яті. Процесор пристосований як для 32-, так і для 64-бітових додатків.

моделі процесора AMD - Athlon 64 для масового ринку і Athlon 64 FX-51 для мультимедіа і професійних додатків (архітектура К8). В системі позначень AMD Athlon 64 має еквівалентну частоту 3200, при фізичної частоті 2 ГГц, FX-51 трохи більше - 2,2 ГГц. Важливе архітектурне нововведення: інтеграція системного контролера пам'яті (system memory controller hub - MCH) безпосередньо в процесор. Це означає, що системна плата (точніше, чіпсет) не повинна більше утримувати окремий чіп контролера Northbridge. Крім того, зникає необхідність в первинної системної шини (FSB) разом з усіма змінами, що вносяться нею затримками. Замість цього К8 використовує HyperTransport (системна шина пропускною спроможністю до 6,4 Гбайт / с) для з'єднання з контролерами Southbridge, AGP або іншими ЦП. Це дозволяє пам'яті працювати з повною частотою процесора, знижує затримки (латентність) і підвищує ефективність пам'яті. Процесор пристосований як для 32-, так і для 64-бітових додатків.

У той же час, коли AMD оголосив Athlon 64, фірма Microsoft заявила про випуск бета-версії Windows XP 64-Bit Edition для 64-бітових процесорів, яка може працювати природно як на процесорах AMD Athlon 64 (ПЕОМ), так і AMD Opteron ( робочі станції).

Робота з прайс-листом

При виборі мікропроцесора необхідно розглядати частину характеристик, наприклад

- Процесори Intel.

- Процесори AMD і Cyrix.

- Сучасні версії процесорів Intel і AMD (відміну від старих).

- Альтернативні фірми-виробники мікропроцесорів.

- Охарактеризувати комплектуючі з прайс-листа

- AMD ATHLON-64 X2 6000+ BOX (ADV6000) 1Мб / 2000МГц Socket AM2

- AMD ATHLON-64 2800 (ADA2800) 512К / 800МГц Socket-754

- Intel Core 2 Duo E6550 2.33 ГГц / 4Мб / 1333МГц 775-LGA

- Intel Pentium 4 1.5 ГГц / 256K / 400MHz 423-PGA

Процесор виконує наступні функції:

1) обчислення адрес команд і операндів;

2) вибірку і дешифрування команд з оперативної пам'яті;

3) вибірку даних з оперативної пам'яті, мікропроцесорної пам'яті і регістрів адаптерів зовнішніх пристроїв;

4) прийом і обробку запитів і команд від зовнішніх пристроїв;

5) обробку даних і їх запис в оперативну пам'ять, регістри мікропроцесора і регістри адаптерів зовнішніх пристроїв;

6) вироблення керуючих сигналів для всіх інших вузлів і блоків комп'ютера;

7) перехід до наступної команді.

Згідно / 4 /, основними параметрами мікропроцесорів є: розрядність, робоча тактова частота, розмір кеш-пам'яті, склад інструкцій, конструктив.

1) Розрядність внутрішніх регістрів - кількість біт, які процесор здатний обробити за один прийом. Розрядність шини даних визначає кількість розрядів, над якими одночасно можуть виконуватися операції. Розрядність шини адреси визначає обсяг пам'яті (адресний простір), з яким може працювати процесор. адресний простір - це максимальна кількість елементів пам'яті, яке може бути безпосередньо адресовано мікропроцесором.

2) Робоча тактова частота (МГц) багато в чому визначає швидкодія процесора, оскільки кожна команда виконується за певну кількість тактів. Чим коротше машинний такт, тим вища продуктивність процесора. Швидкодія комп'ютера також залежить і від тактової частоти шини системної плати, з якої працює процесор.

3) Кеш-пам'ять, Що встановлюється на платі мікропроцесора, має два рівні:

3.1) L 1 - пам'ять першого рівня, що знаходиться всередині основної мікросхеми (ядра) процесора і працює завжди на повній частоті процесора (вперше з'явилася в мікропроцесорах Intel 386SLC і 486).

3.2) L 2 - пам'ять другого рівня, кристал, що розміщується на платі мікропроцесора і пов'язаний з ядром внутрішньої шиною (вперше введена в мікропроцесорах Pentium II). Ця пам'ять може працювати на повній або половинній частоті процесора.

4) склад інструкцій - перелік, вид і тип команд, автоматично виконуваних мікропроцесором. Визначає безпосередньо ті процедури, які можуть виконуватися над даними і ті категорії даних, над якими можуть виконуватися ці процедури. Істотна зміна складу інструкцій відбулося в мікропроцесорах Intel 80386 (цей склад прийнятий за базовий), Pentium MMX, Pentium III, Pentium 4.

5) конструктив має на увазі ті фізичні роз'ємні з'єднання, в які встановлюється мікропроцесор. Різні роз'єми мають різну конструкцію (щілинний роз'єм - Slot, роз'єм-гніздо - Soket), різну кількість контактів.

Процесори класифікуються за різними ознаками. Відповідно до / 4, 13 /, можна виділити наступні основні ознаки:

1) По призначенням мікропроцесори діляться на універсальні і спеціалізовані. Перші призначені для вирішення широкого кола завдань, в системі команд закладена алгоритмічна універсальність. Таким чином, продуктивність процесора слабо залежить від специфіки вирішуваних завдань. Спеціалізовані процесори призначені для вирішення певного кола завдань або навіть одного завдання, мають обмежений набір команд. Серед них виділяються процесори для обробки даних, математичні процесори і мікроконтролери.

2) За кількості виконуваних програм процесори поділяються на однопрограмні (Перехід до виконання наступної програми відбувається тільки після завершення поточної програми) і мультипрограмному (Одночасно виконуються декілька програм).

3) По структурному ознакою виділяють мікропроцесори з фіксованою розрядністю (Мають строго певну розрядність) і мікропроцесори з нарощуваний розрядністю (Дозволяють секціями збільшувати число розрядів).

4) За числу БІС (НВІС) в микропроцессорном комплекті можна виділити однокристальних, багатокристальні і багатокристальні секційні процесори. У першому випадку все апаратні частини процесора реалізовані у вигляді однієї БІС (НВІС); можливості таких процесорів обмежені ресурсами кристала і корпуса. Багатокристальні процесори виходять в результаті розбиття логічної структури процесора на функціонально закінчені частини, кожна з яких реалізована у вигляді БІС чи СБИС. В останньому випадку функціонально закінчені частини логічної структури процесора розбиваються на секції, які реалізовані у вигляді БІС.

5) За розрядності оброблюваної інформації мікропроцесори можуть бути 4, 8, 12, 16, 24, 32 і 64-розрядними. На практиці найбільшого поширення мають 32-розрядні процесори; все більше застосування знаходять 64-розрядні процесори.

6) По виду технології виготовлення БІС (НВІС) мікропроцесори діляться на дві групи: процесори, побудовані на БІС, виготовлених за уніполярної технології, І процесори, побудовані на БІС, виготовлених за біполярної технології. Представники першої групи: p-канальні (p-МОП), n-канальні (n-МОП), компліментарні (КМОП) БІС. (МОП - метал-окисел-провідник). До другої групи належать БІС на базі транзісторно- транзисторної логіки (ТТЛ), емітерний-зв'язаної логіки (ЕСЛ) і інтегральної инжекторной логіки (І 2 Л). Вид технології виготовлення БІС багато в чому визначає ступінь інтеграції мікросхем, швидкодія, енергоспоживання, перешкодозахищеність і вартість процесорів. По комплексу цих ознак можна віддати перевагу мікропроцесорах, виконаним за n-МОП і КМОП- технологіями, які забезпечують високу щільність компонування, високу швидкодію і відносно малу вартість. ЕСЛ забезпечує найвищу швидкодію процесорів, але низьку щільність компонування і високе енергоспоживання. Технологія І 2 Л дає усереднені характеристики мікропроцесорів.

7) По характером системи команд виділяють процесори з повним набором інструкційабо CISCПроцесор (Complex Instruction Set Command), процесори зі скороченим набором інструкцій або RISCПроцесор (Reduced Insrruction Set Command), процесори з надвеликих командним словом або VLIWПроцесор(Very Long Instruction Word). CISC-процесори мають великий набір різноформатних команд, що дозволяє застосовувати ефективні алгоритми вирішення завдань, але, в той же час, ускладнює схему процесора, і в загальному випадку не забезпечує максимального швидкодії. Архітектура CISC властива класичним процесорам. RISC-процесори містять набір простих, найчастіше зустрічаються в програмах інструкцій. При необхідності виконання більш складних команд в процесорі проводиться їх автоматичне прибирання з простих команд. Всі прості команди мають однаковий розмір і на їх виконання витрачається один машинний такт (на виконання найкоротшою команди з системи CISC зазвичай витрачається чотири такту). Сучасні 64-розрядні RISC-процесори випускаються багатьма фірмами: Apple (PowerPC), IBM (PPC) тощо У VLIW-процесорах одна інструкція містить кілька операцій, які повинні виконуватися паралельно. Завдання розподілу роботи між декількома обчислювальними пристроями процесора вирішується під час компіляції програми. Такий підхід дозволили зменшити габарити процесорів і споживання енергії. Прикладами VLIW-процесорів служать Itanium фірми Intel, McKinley фірми Hewlett-Packard і інші.

8) По числу і способу використання внутрішніх регістрів розрізняють акумуляторні, многоаккумуляторние і стекові процесори. акумуляторні процесори - це процесори з одним регістром результату. Їх відмітною характеристикою є відносна простота апаратної реалізації, а також спрощений формат команд (будуть розглянуті в наступній лекції). У командах адресу операнда в акумуляторі не вказується, а адресується тільки другий операнд. Недоліками таких процесорів є необхідність попереднього завантаження операнда в акумулятор перед виконанням операції і неможливість безпосереднього запису результату виконання команди в довільну комірку пам'яті або регістр. В многоаккумуляторнихрегістрах, якими є більшість сучасних процесорів, функції регістрів результату може виконувати будь-який регістр загального призначення або елемент пам'яті. У командах обидва операнда задаються явно, а результат операції найчастіше поміщається на місце одного з операндів. В стекових процесорах зазвичай використовується великий апаратний стек і додатковий зовнішній стек в пам'яті (при нестачі апаратного). Завдяки спеціальному розміщенню операндів в стеці обробку інформації можна виконувати безадресними командами, що дозволяє підвищити продуктивність процесора і економити пам'ять. Такі команди витягують з стека один або два операнда, виконують над ними відповідну арифметичну або логічну операцію і заносять результат в вершину стека. Недоліком є необхідність попередньої підготовки даних, що використовують адресні команди.

З історією розвитку процесорів і їх порівняльною характеристикою більш детально можна ознайомитись в / 4, 13 /. Далі розглянемо фізичну і функціональну структуру процесора.

Фізична і функціональна організація ЦП (на прикладі ЦП Intel 8086). ШИ.

Фізична структура процесора є досить складною. Відповідно до / 4 /, ядро процесора містить головний керуючий і виконують модулі - блоки виконання операцій над цілочисельними даними. До локальних керуючим схемами відносяться: блок з плаваючою комою, модуль пророкування розгалужень, регістри мікропроцесорної пам'яті, регістри кеш-пам'яті 1-го рівня, шинний інтерфейс і багато іншого.

Примітка: Під логічним ядром розуміється схема, по якій зроблений процесор. Фізично ядро являє собою кристал, на якому за допомогою логічних елементів реалізована принципова схема процесора.

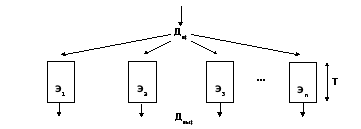

У найзагальнішому випадку функціональну структуру процесора можна представити у вигляді композиції, згідно з одними джерелами / 4, 5 /, двох частин: операційного пристрою (ОУ) і шинного інтерфейсу (ШИ), Згідно з іншими / 2 /, - трьох блоків: операційного блоку (ПРО), керуючого блоку (УБ) і интерфейсного блоку (ІБ). Наявні незначні розбіжності в кількості і назві блоків жодним чином не порушують число і принципи функціонування компонентів процесора. Тому розглянемо перший (більш наочний) варіант з джерела / 4 /.

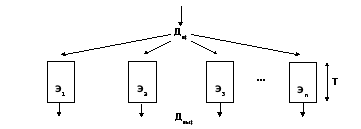

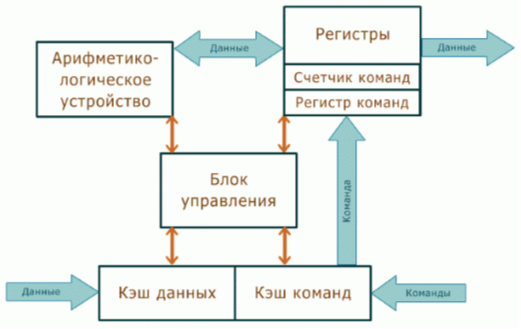

Спрощена типова структура процесора представлена на малюнку 4.1.

ОУ містить пристрій управління (УУ), арифметико-логічний пристрій (АЛП), регістр прапорів, регістри загального призначення (РОН), регістри-покажчики, індексні регістри. ШИ містить адресні регістри, блок регістрів (буфер) команд, вузол формування адреси, схеми управління шиною і портами. Обидві частини мікропроцесора працюють паралельно, причому ШИ працює швидше ОУ. Розглянемо ці блоки процесора більш докладно.

ШИпризначений для зв'язку і узгодження мікропроцесора з системною шиною комп'ютера, а також для прийому, попереднього аналізу команд виконуваної програми і формування повних адрес операндів і команд.

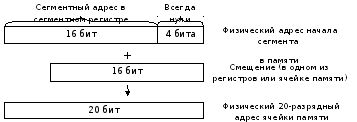

сегментні (Адресні) регістри спільно з вузлом формування адреси реалізують сегментацію пам'яті. Команди і дані зберігаються в осередках, і їх місце розташування в пам'яті визначається адресами відповідних осередків. Оскільки команди і дані на рівні кодів не відрізняються один від одного, то для відмінності команд і даних використовується їх розміщення в різних областях пам'яті - сегментах. сегмент - це прямокутна область пам'яті, що характеризується початковим адресою і довжиною. Початкова адреса (адреса початку сегмента) - це номер (адреса) осередки пам'яті, з якої починається сегмент. довжина сегмента – це кількість вхідних в нього елементів пам'яті. Сегменти можуть мати різну довжину. Всі осередки, розташовані всередині сегмента, перенумеровуються, починаючи з нуля. Адресація осередків всередині сегмента ведеться щодо початку сегмента; адреса комірки в сегменті називається зміщеннямабо ефективним адресою -EA(Щодо початкової адреси сегмента). Поточний сегмент можна вказати за допомогою завантаження відповідного сегментного регістра:

1) CS (Code Segment) - визначає початок поточного сегмента коду, в якому розташовуються команди програми. Вибірка команди виробляється з використанням в якості ефективного адреси вмісту регістра IP (Instruction Pointer) , А в якості адреси сегмента - вмісту CS. Саме регістр IP зберігає зсув адреси поточної команди програми.

2) DS (Data Segment) - визначає початок поточного сегмента даних. Посилання на дані (за деяким винятком) здійснюються щодо вмісту цього регістра.

3) SS (Stack Segment) - визначає початок поточного сегмента стека. Як правило, всі адреси даних, пов'язаних зі стеком, задаються щодо вмісту цього регістра.

4) ES (Extended Segment) - визначає початок додаткового поточного сегмента, який зазвичай розглядається як допоміжний сегмент даних (при міжсегментних пересиланнях).

Вузол формування адреси і регістр команд функціонально входять до складу УУ і були розглянуті вище.

При адресації пристроїв введення-виведення (УВВ) сегментні регістри не використовуються. Взаємодія з ними процесор здійснює через спеціальне адресний простір - порти. Кожен порт має номер, що відповідає адресі підключеного до нього пристрою. Порту пристрою відповідає апаратура сполучення і два регістра - для обміну даними та інформацією, що управляє. Схема управління шиною і портами виконує наступні функції:

1) формування адреси порту і керуючої інформації для нього;

2) прийом керуючої інформації від порту, інформації про готовність порту і його стан;

3) організація наскрізного каналу в системному інтерфейсі для передачі даних між портом УВВ і процесором.

Схема управління шиною і портами використовує для зв'язку з портами системну шину: шину адреси, шину даних і шину інструкцій.

Фізична і функціональна організація ЦП (на прикладі ЦП Intel 8086). ОУ.

В цілому ОУ виконує операції, які визначаються командами, і формує ефективні адреси.

УУ виробляє керуючі сигнали, що надходять в усі блоки обчислювальної машини. У складі УУ можна виділити наступні функціональні блоки:

1) регістр команд - запам'ятовує регістр, в якому зберігається код команди: код операції і адреси операндів (розташований в інтерфейсній частини процесора);

2) дешифратор операцій - логічний блок, який відповідно до надходять з регістра команд кодом операції вибирає один з безлічі наявних у нього виходів;

3) постійний запам'ятовуючий пристрій (ПЗУ) мікропрограм зберігає керуючі імпульси для виконання в блоках обчислювальної машини процедур обробки інформації; імпульс за обраним дешифратором операцій проводу зчитує з ПЗУ мікропрограм необхідну послідовність керуючих сигналів;

4) вузол формування адреси (Розташовується в ШИ) - пристрій для обчислення повної адреси осередки пам'яті (регістра) за реквізитами, що надходять з мікропроцесорної пам'яті або регістра команд;

5) кодові шини даних, адреси і інструкцій - частина внутрішньої інтерфейсної шини процесора.

Таким чином, УУ формує керуючі сигнали для виконання процесором своїх функцій, розглянутих вище.

Малюнок 4.1 - Спрощена типова структура процесора

АЛУ призначене для виконання арифметичних і логічних операцій перетворення інформації. Функціонально в найпростішому варіанті АЛУ складається з наступних компонент:

1) суматор виконує процедуру складання двійкових кодів, має розрядність подвійного машинного слова (32 біта);

2) регістри - швидкодіючі комірки пам'яті різної довжини: регістр 1 має розрядність 32 біта, регістр 2 - 16 біт; при додаванні в регістр 1 поміщається перший доданок, а потім результат, в регістр 2 - другий доданок;

3) схема управління приймає по кодовою шинам інструкцій керуючі сигнали від УУ і перетворює в сигнали для керування роботою регістрів і суматора.

АЛУ виконує арифметичні операції тільки над двійковими числами з фіксованою точкою. Для обробки чисел з плаваючою точкою залучається математичний співпроцесор або спеціально складені програми.

Більш докладні відомості про пристрій і функціонування УУ і АЛУ можна знайти в / 3 - 5 /.

регістри ОУ - частина мікропроцесорної пам'яті. Розглянемо регістри на прикладі базового процесора Intel 8086, який містить всього 14 двобайтових регістра. У сучасних процесорах їх набагато більше і більшої розрядності. Однак в якості базової моделі, зокрема для мови Асемблера, використовується 14-реєстрова пам'ять процесора.

До складу ОУ входять такі регістри:

1) регістри загального призначення (РОН) або універсальні: AX - (AH, AL), BX - (BH, BL), CX - (CH, CL), DX - (DH, DL) можуть використовуватися для тимчасового зберігання будь-яких даних, при цьому можна працювати з кожним регістром цілком, а можна окремо, з кожної його половиною; але кожен з РОН може використовуватися і як спеціальний при виконанні деяких конкретних команд;

2) регістри зсувів: SP, BP, SI, DI є неподільними і призначені для зберігання відносних адрес комірок пам'яті всередині сегментів (зсувів щодо початку сегментів);

2.1) SP (Stack Pointer) - зміщення вершини стека;

2.2) BP (Base Pointer) - зміщення початкового адреси поля пам'яті, безпосередньо відведеного під стек;

2.3) SI (Source Index) , DI (Destination Index) призначені для зберігання адрес індексу джерела і приймача даних при операціях над рядками і їм подібних.

Слово стану процесора (PSW – Processor State Word) або регістр прапорів - має розмір 2 байти і містить однорозрядні ознаки або прапори. Всього в регістрі 9 прапорів: 6 з них умовні або статусні, Відображають результати операцій, виконаних ОУ, інші 3 керуючі, Визначають режим виконання програми.

1) Статусні прапори.

1.1) CF (Carry Flag) - прапор переносу. Встановлюється в 1, якщо при виконанні арифметичних і деяких операцій зсуву виникає «перенесення» зі старшого розряду.

1.2) PF (Parity Flag) - прапор парності. Перевіряє молодші 8 бітів результатів над даними. Парне число одиниць призводить до установки цього прапора в 1, непарне - в 0.

1.3) AF (Auxiliary Carry Flag) - прапор логічного перенесення в двійковій-десяткового арифметиці. Встановлюється в 1, якщо арифметична операція приводить до переносу або позики четвертого праворуч біта однобайтового операнда. Використовується при арифметичних операціях над двійковій-десятковими кодами і кодами ASCII.

1.4) ZF (Zero Flag) - прапор нуля. Встановлюється в 1, якщо результат операції дорівнює 0, в іншому випадку ZF обнуляється.

1.5) SF (Sign Flag) - прапор знака. Встановлюється в 1, якщо результат арифметичної операції є негативним, в 0, якщо результат позитивний.

1.6) OF (Overflow Flag) - прапор переповнення. Встановлюється в одиницю при арифметичному переповненні, коли результат виходить за межі розрядної сітки.

2) Керуючі прапори.

2.1) TF (Trap Flag) - прапор трасування. Одиничний стан цього прапора переводить процесор в режим покрокового виконання програми.

2.2) IF (Interrupt Flag) - прапор переривань. При нульовому стані цього прапора переривання заборонені, при одиничному - дозволені (про механізм переривань мова піде в наступній лекції).

2.3) DF (Direction Flag) - прапор напрямку. Використовується в строкових операціях для завдання напряму обробки даних; при одиничному стану рядки обробляються «справа наліво», при нульовому - «зліва направо».

Розташування прапорів в регістрі PSW показано на малюнку 4.2. Вільні біти відведені для використання в майбутньому.

Малюнок 4.2 - Схема розташування прапорів в регістрі PSW

Архітектурні принципи організації RISC-процесорів.

Як наголошується в / 2, 14, 15 /, список команд сучасного мікропроцесора може містити досить велике число команд. Однак не всі вони використовуються однаково часто і регулярно. Це властивість системи команд стало передумовою для розвитку процесорів з RISC-архітектурою. Основна ідея полягала в скороченні списку використовуваних команд і, внаслідок цього, спрощення керуючого блоку процесора і для організації більш швидкого виконання команд, що залишилися за рахунок звільнених при цьому ресурсів кристала.

Перші процесори RISC-були реалізовані на початку 80-х років 20 століття / 2 /:

1) У 1980 році в каліфорнійському університеті міста Берклі під керівництвом професорів Давида Паттерсона (David Patterson) і Карло Секуін (Carlo Sequin) був розроблений процесор, який отримав назву RISC. Були розроблені моделі RISC-I, RISC-II, SOLAR.

2) У 1981 році в університеті міста Стенфорда під керівництвом Джона Хеннесі (Dohn Hennesy) був спроектований процесор, який отримав назву MIPS (Microprocessor Without Interlocked Pipeline Stages - мікропроцесор без блокування конвеєра). Більш докладно про суть конвейеризации буде розглянуто в наступному питанні лекції.

Пізніше обидві моделі RISC-стали називати RISC-процесорами. Відмінною особливістю цих процесорів є велика кількість РОН (близько 256).

Коротко охарактеризуємо основні принципи RISC-архітектури / 2, 15 /.

1) Однакова довжина команд. Це полегшує їх вибірку з основної пам'яті. Всі команди зчитуються за один такт, що дозволяє обробляти потік командних інструкцій по конвеєрним принципом, тобто виконується синхронізація апаратних частин процесора з урахуванням послідовної передачі управління від одного апаратного блоку до іншого. В сучасних RISC-процесорах довжина команди складає 32 біта.

2) Скорочений набір дій над операндами, розміщеними в пам'яті. Прості способи адресації пам'яті забезпечують швидкий доступ до операндам в пам'яті. Обробка даних, реалізована при виконанні команд RISC, ніколи не поєднується з операціями читання (записи) пам'яті (на відміну від багатьох команд CISC). Обмін операндами між пам'яттю і регістрами виконується спеціальними командами завантаження (LOAD) і запам'ятовування (STORE). Велика кількість регістрів блоку РОН дозволяє зменшити число звернень до пам'яті.

3) Виконання всіх обчислювальних операцій над даними, розміщеними тільки в РОН. Оскільки регістрів багато, то все скалярні змінні і навіть невеликі масиви змінних найчастіше розміщуються в регістрах, що дозволяє прискорити обробку даних. Використання простих команд спрощує реалізацію їх конвеєрної обробки. В середньому команди RISC виконуються за один такт.

4) Відносно прості схеми управління. Зменшення списку команд, використання команд, що реалізують тільки прості операції, виключення в командах обробки даних звернень до пам'яті дозволили зменшити витрату ресурсів кристала на управління. Завдяки цьому велика площа кристала виділяється для розміщення пристроїв, що дозволяють збільшити загальну продуктивність процесора: додаткових конвеєрів, збільшеною кеш-пам'яті 1-го рівня, більшого числа РОН.

Важливо відзначити, що при однаковій технології виробництва RISC-процесори мають більш високі частоти роботи в порівнянні з CISC-процесорами, що є важливою перевагою RISC-процесорів.

Згідно / 15 /, в архітектурі RISC-процесорів можна виділити наступні апаратні блоки, що утворюють ступені конвеєра:

1) Блок завантаження інструкцій включає в себе наступні складові частини: блок вибірки інструкцій з пам'яті, регістр інструкцій, куди поміщається команда після вибірки і блок декодування інструкцій. Цей ступінь називається щаблем вибірки інструкцій.

2) РОН спільно з блоками управління регістрами утворюють другу сходинку конвеєра, яка відповідає за читання операндів команд. Операнди можуть зберігатися в самій команді або в одному з РОН. Цей ступінь називається щаблем вибірки операндів.

3) АЛУ і, якщо в цій архітектурі реалізований акумулятор, разом з логікою управління, Яка виходячи з вмісту регістра інструкцій визначає тип виконуваної мікрооперації. При виконанні операцій умовного і безумовного переходів джерелом даних може бути також лічильник команд. Дана щабель називається виконавчої щаблем конвеєра.

4) Набір з РОН і логіки записи утворюють щабель збереження даних. Тут результати виконання команд записуються в РОН або основну пам'ять.

До RISC-процесорів зараховують мікропроцесори MIPS R4000, R8000, R100000 фірми MIPS Technologies Inc., UltraSPARC I, UltraSPARC II, UltraSPARC III фірми Sun, PowerPC фірми IBM-Motorola, Alpha AXP фірми DEC, PA-RISC фірми Hewlett Packard, мікроконтролери фірми Microchip .

Незважаючи на очевидні переваги, RISC-процесори «в чистому вигляді» не набули широкого поширення на ринку персональних комп'ютерів, більшість з них використовується в якості центральних процесорів робочих станцій. Однак більшість сучасних CISC-процесорів, наприклад, Pentium, використовують досягнення RISC-архітектур, зокрема, RISC-ядра для виконання обчислювальних операцій.

Моделі RISC-процесорів активно розвиваються і удосконалюються. В даний час на їх основі реалізуються комерційно важливі продукти: SPARC- і MIPS-системи.

Більш повні відомості про RISC-процесорах, особливості їх архітектури і функціонування можна знайти в / 2 /, спеціальній літературі і відкритих джерелах мережі Інтернет.

Архітектурні способи підвищення продуктивності процесорів. Конвеєрна обробка інформації.

Продуктивність є однією з найбільш важливих характеристик процесора. Згідно / 2 /, в загальному випадку вона визначається кількістю обчислювальної роботи, що виконується в одиницю часу. До найважливіших чинників, що впливає на продуктивність, відносяться тактова частота, число команд програми, середній час виконання окремої команди. Для спрощеної оцінки продуктивності процесора часто використовують показник, який вказує число команд, виконуваних за секунду. Він визначається як частка від ділення тактової частоти на середній час виконання процесором окремої команди і вимірюється в MIPS (Meg Insruction Per Second) для цілочисельних задач і MFLOPS (Meg Floating Point Operations Per Second) для обчислень з плаваючою точкою. При цьому оцінки показника, що визначає число команд, виконуваних за секунду, проводять для операцій з реєстровими операндами, не прив'язуючись до швидкодії основної пам'яті. Однак цей показник не враховує особливості архітектури конкретних процесорів. Тому для порівняльних характеристик різних процесорів використовуються відносні оцінки продуктивності, для отримання яких використовуються спеціальні тестові програми.

Відповідно до / 2 /, підвищення продуктивності процесорів в більшості випадків досягається за рахунок застосування спеціальних технологічних і архітектурних рішень. Технологічні підходи (вдосконалення технологій виробництва ІС, збільшення ступеня інтеграції) були розглянуті раніше, у другому розділі. Тому докладніше зупинимося на архітектурних способах підвищення продуктивності процесорів. Удосконалення архітектури процесорів, що забезпечує підвищення його продуктивності, в даний час пов'язано, перш за все, з розвитком засобів паралельної обробки даних. Тут можна виділити наступні напрямки:

1) Збільшення «природного» паралелізму - підвищення розрядності обробки і передачі даних (розрядність процесорів підвищилася з 4 до 32 і 64 розрядів).

2) Конвеєрна (багатофазна) обробка даних - обчислювальний процес ділиться на кілька фаз, для кожної з яких використовуються свої кошти і буфер для зберігання результату (ступінь конвеєра).

3) Багатоелементна обробка даних - паралельна обробка даних в декількох операційних блоках (ОУ) процесора.

Способи паралельної обробки можуть поєднуватися. Наприклад, в одному процесорі можна організувати кілька операційних блоків, в кожному з яких використовувати конвейеризацию.

Розглянемо більш детально два інших напрями.

при багатофазної обробці, як показано на малюнку 4.3, процес обробки даних розбивається на кілька стадій (фаз), які виконуються послідовно.

Малюнок 4.3 - Багатофазна обробка даних

Між фазами є буфери для зберігання проміжних результатів. Після виконання першої фази результат запам'ятовується в буфері і починається обробка другої фази. Засоби виконання першої фази звільняються, і на них надходить наступна порція даних. Якщо тривалість фаз обробки однакова і становить T/ n, То при такому способі продуктивність системи збільшиться в n раз. Цей спосіб відповідає конвеєрної обробці.

Розглянемо організацію конвеєра на рівні виконання машинної команди / 2 /. Кожен блок в конвеєрної ланцюжку здійснює тільки один етап виконання команди. Повна обробка команди займає кілька тактів.

Типові етапи виконання команди: 1) вибірка команди IF (Instruction Fetch), 2) дешифрування команди ID (Instruction Decode), 3) читання операндів RD (Read Memory), 4) виконання заданої в команді операції EX (Execute), 5) запис результату WB (Write Back). В ході виконання команда просувається по конвеєру, звільняючи чергову сходинку для наступної команди. Вміст буферів, які використовуються для зберігання інформації, переданої по східцях конвеєра, оновлюється в кожному такті по завершенню етапу виконання чергової команди. Проміжні буфери забезпечують паралельну незалежну роботу блоків конвеєрної ланцюжка: в той час, коли наступний блок починає виконувати етап чергової команди, попередній блок може приступати до обробки наступної команди, що демонструє малюнок 4.4.

|

Такти роботи процесора |

||||||||||

|

команда i | ||||||||||

|

команда i + 1 | ||||||||||

|

команда i + 2 | ||||||||||

|

команда i + 3 | ||||||||||

|

команда i + 4 | ||||||||||

|

команда i + 5 | ||||||||||

Малюнок 4.4 - Конвеєрна обробка команд

Слід зазначити, що конвеєрна обробка команд не зменшує час виконання окремої команди, яке в конвеєрному процесорі залишається таким же, як і в звичайному неконвейерном. Однак завдяки тому, що при конвеєрної обробці велика частина обчислювального процесу в режимі одночасного виконання команд, швидкість видачі результатів послідовно виконуваних команд збільшується пропорційно числу ступенів конвеєра. Тривалість виконання окремих етапів виконання команди в загальному випадку залежить від типу команди і місця розміщення операндів. Конвеєрна обробка команд найбільш ефективна в тому випадку, якщо тривалість всіх фаз виконання команди приблизно однакова. На жаль, забезпечити безперервну роботу конвеєра не завжди вдається через різні конфліктів: по ресурсах, за даними, з управління. Більш докладно про конфлікти - в / 2, 7 /.

Процесор, в якому процес виконання команди розбивається на 5-6 ступенів, називається звичайним конвеєрним процесором. Якщо збільшити кількість щаблів конвеєра, то кожна окрема ступінь виконуватиме меншу роботу, а, отже, утримувати менше апаратної логіки. Завдяки більш коротким затримкам поширення сигналів в кожній окремо взятій ступені конвеєра досягається підвищення частоти роботи і відповідне підвищення продуктивності процесора. Процесор, який має конвеєр істотно глибше 5-6 ступенів, називається суперконвейерная. Наприклад, Pentium II містить 12 ступенів, UltraSPARC III - 14 ступенів, Pentium 4 - 20 ступенів.

багатоелементна

T і в системі використовується n T/ n

A = B + C; D = E + F.

суперскалярніскалярноюскалярними

Архітектурні способи підвищення продуктивності процесорів. Багатоелементна обробка інформації.

Як показано на малюнку 4.5 / 2 /, багатоелементна обробка здійснюється на декількох паралельно працюючих ОУ. Кожен елемент виконує свою роботу, здійснюючи обробку порції даних від початку до кінця.

Малюнок 4.5 - Багатоелементна паралельна обробка даних

Якщо час виконання роботи на окремому елементі становить T і в системі використовується n елементів, то при певній ідеалізації можна очікувати, що середній час виконання такої роботи складе T/ n (Реально - менше). У сучасних процесорах такий спосіб обробки пов'язаний з поняттям суперскалярной архітектури.

Найпростішим прикладом обчислювального паралелізму є виконання двох команд, операнди яких не пов'язані між собою:

A = B + C; D = E + F.

Тому обидві команди можна виконувати одночасно. Для виконання незв'язаних операцій до складу процесора включають набір арифметичних пристроїв, кожне з яких зазвичай має конвеєрну організацію.

Процесор, що містить кілька ОУ, які забезпечує одночасне виконання більш однієї скалярної команди, називається суперскалярні процесором. команда називається скалярною, Якщо її вхідні операнди і результат є числами (скалярами). Традиційні процесори з одним ОУ називаються скалярними. У суперскалярного процесорі обробка команд распараллелена не тільки в часі (конвеєр), але і в просторі (кілька конвеєрів). Продуктивність такого процесора оцінюється темпом сходу виконаних команд з усіх його конвеєрів.

В даний час використовуються два способи суперскалярной обробки. Перший спосіб базується на чисто апаратному механізмі вибірки незв'язаних команд програми з пам'яті (кеш-пам'яті, буфера передвибірки) і паралельному запуску їх на виконання. Відповідальність за ефективність завантаження паралельно функціонуючих конвеєрів покладається на апаратні засоби процесора, що є основною перевагою цього способу суперскалярной обробки. В цьому випадку процес трансляції програм для суперскалярного процесора нічим не відрізняється від трансляції програм для традиційного скалярного процесора. Відповідно до цього способом, порівняно легко реалізуються суперскалярні мікропроцесори різних сімейств програмно сумісні між собою. При цьому не виникає проблем з використанням раніше створеного програмного забезпечення. Всі процесори сімейства Pentium реалізовані за цим способом.

У процесорах, що реалізують другий спосіб суперскалярной обробки, планування паралельного виконання кількох команд покладається на распараллелівающій компілятор. Спочатку він аналізує вихідну програму з метою виявлення команд, які можуть виконуватися одночасно. Потім компілятор групує такі команди в пакети команд - довгі командні слова (VLIW), причому, число простих команд в команді VLIW приймається рівним числу виконавчих блоків процесора. Оскільки всю роботу по підготовці до виконання VLIW-команд виконує компілятор, конфліктні ситуації при їх виконанні виключаються. Такий спосіб суперскалярной обробки реалізується в VLIW-процесорах, що мають статичну сперскалярную архітектуру. На жаль, для таких процесорів потрібне спеціальне програмне забезпечення. Крім того, програми, скомпільовані для одного покоління мікропроцесорів, можуть виконуватися неефективно без перекомпіляції на процесорах наступного покоління. Це вимагає від розробників програмного забезпечення розробки модифікованих версій виконуваних файлів свого продукту для різних поколінь процесорів. Ідеї VLIW запропоновані російськими інженерами і вченими на чолі з професором Б.А. Бабаяном при розробці вітчизняної супер-ЕОМ «Ельбрус-3» (1990). В даний час VLIW-технологія реалізована в процесорі Ельбрус Е2К вітчизняної компанії «Ельбрус Інтернешнл», процесорах Crusoe фірми Transmeta, а також в сімействі сигнальних процесорів (для цифрової обробки сигналів) TMS320C60xx фірми Texas Instruments.

Класифікація і структура команд процесора.

За функціональною ознакою всі команди процесора можна розділити на наступні групи:

1) команди пересилання даних і введення-виведення;

2) команди арифметичних і порозрядних логічних операцій;

3) команди передачі управління.

Команди пересилання даних забезпечують обмін інформацією між регістрами мікропроцесора, а також зовнішні обміни даними при передачі в процесор з пам'яті або пристрою введення і з процесора в пам'ять або пристрій виводу. У цих командах зазвичай вказується напрямок передачі, джерело і (або) приймач даних. Наприклад, в мові Асемблера, до командам цієї групи можна віднести команду пересилання MOV, Команду завантаження LOAD, Команди записи в порт і читання з порту УВВ, IN і OUT, Відповідно т.п. Також сюди часто включають команди переміщення даних в стек PUSH і вилучення даних з стека POP.

У число команд арифметичних і порозрядних логічних операцій в більшості випадків входять команди найпростіших арифметичних операцій, наприклад, ADD (скласти), SUB (відняти), і логічних операцій, наприклад, AND ( «І»), OR ( «АБО») і т.п. До арифметичним командам також відносять команди арифметичних і логічних зрушень, а до команд логічних операцій - команди порівняння COMPARE (неруйнівного віднімання). У число команд цієї групи можуть входити команди складних арифметичних операцій: множення, ділення (є не у всіх процесорах), команди обробки даних з плаваючою точкою, команди мультимедійної обробки.

Команди передачі управління використовуються для зміни послідовності виконання команд при наявності програмних розгалужень: команд умовних і безумовного (JMP) переходів, зверненні до підпрограм (CALL) і виходу з них (RETURN). Команди умовних переходів реалізують передачі управління в залежності від значення прапорів в регістрі PSW. З їх допомогою процесор одну з можливих гілок продовження програми. Зазвичай в системі команд є кілька команд умовних переходів.

У сучасних процесорах системи команд поряд з традиційними командами, переліченими вище, містять в своєму складі групи команд, що розширюють функціональні можливості мікропроцесора з обробки інформації, управління його роботою, а також забезпечують реалізацію многозадачного захищеного режиму роботи.

В системи команд конкретних процесорів можуть входити команди, які не вписуються в запропоновану класифікацію. Подібні команди не відображають загальних принципів побудови програм і розглядаються як додаткові.

Виконання команди (машинної операції) розділене на більш дрібні етапи - микрооперации (мікрокоманд), під час яких виконуються певні елементарні дії. Конкретний склад микроопераций визначається системою команд і логічною структурою обчислювальної машини. Послідовність мікрокоманд, що реалізують цю операцію (команду), утворює микропрограмму операції. Інтервал часу, протягом якого виконується одна або одночасно кілька мікрооперацій, називається машинним тактом. Межі тактів задаються синхросигналами, які виробляються генератором синхросигналов.

У загальному випадку команда мікропроцесора містить дві частини: операційну та адресну. Відповідно до / 1 /, угоду про розподіл розрядів між цими частинами команди і про спосіб кодування інформації визначає структуру (формат) команди. В операційній частини команди міститься код операції, що забезпечує кодування операцій (де n - число двійкових розрядів, відведених під операційну частину команди) і визначає, які при цьому будуть задіяні пристрої в процесорі або поза ним. В k-розрядної адресній частині команди міститься інформація про адреси операндів, що беруть участь у виконанні операції. У загальному випадку адресна частина команди повинна містити чотири адресних поля A1 , A2 , A3 , A4 . Вони призначені для завдання адрес операндів (A1, A2), адреси результату (A3) та адреси наступної команди (A4). Як адрес A1, ..., A3 можуть використовуватися адреси осередків оперативної пам'яті і адреси регістрів мікропроцесорної пам'яті, як адресу A4- тільки адреси осередків оперативної пам'яті. При використанні повного набору адрес формат команди виявляється громіздким. Було відзначено, що не для всіх операцій необхідний повний набір адрес A1-A4. Залежно від зазначених вище числа адрес команди поділяються на 0-адресні (безадресні), 1-адресні, 2-адресні, 3-адресні і 4-адресні.

Практично у всіх мікропроцесорах виключений адреса A4. Це обумовлено тим, що більшість команд відносяться до лінійних ділянок алгоритмів, і такі команди можуть бути розміщені в осередках пам'яті з послідовно зростаючими адресами. У цьому випадку для отримання адреси наступної команди до початкового адресою сегмента коду досить додати її зміщення в сегменті коду, що зручно реалізувати за допомогою покажчика команд. Такий спосіб адресації команд називається природним, А реалізують його процесори називаються процесорами з природним способом адресації команд. При порушенні природного порядку проходження команд (розгалуження, циклах) використовуються спеціальні команди передачі управління, в яких міститься адреса переходу, але не використовуються адреси операндів. Процесори, в адресному полі команд яких використовується адреса A4, називаються процесорами з примусовим способом адресації команд.

Використання адреси результату A3 в багатьох випадках також виявляється надлишковим. Це обгрунтовується тим, що результат арифметичних і логічних операцій над двома операндами зазвичай може бути поміщений на місце одного з операндів, який в подальшому, швидше за все, використовуватися не буде. При цьому в 2-адресних командах в адресне поле необхідно вводити додаткові розряди, що показують, хто з них є джерелом, а хто - приймачем інформації. У процесорах з акумуляторної архітектурою число адрес в адресній частині команди зменшено до одного. У них один з операндів, розміщених в акумуляторі, неявно задається кодом команди, і результат поміщається в акумулятор.

У безадресних командах здійснюється неявне завдання операнда. До таких командам відносяться команди управління процесором (наприклад, пуску, зупинки і т.д.), команди для роботи зі стеком (операнд, адресований покажчиком SP, неявно задається кодом команди). Безадресні команди мають гранично скорочений формат, але не можуть самостійно утворити функціонально повну систему команд і застосовуються тільки разом з адресними.

Формат команд впливає на час вирішення завдань, витрати пам'яті, складність процесора і залежить від класу вирішуваних завдань. Зокрема, для науково-технічних розрахунків, в яких великий обсяг займають багатокрокові обчислення, більш ефективними виявляються 1-адресні команди, а при використанні стекового процесора - і безадресні команди. Для завдань управління, де велику частку складають пересилання і логічні операції ефективними є 2-адресні команди. Виходячи зі сказаного вище, слід зазначити, що в сучасних процесорах зазвичай використовуються безадресні, 1-адресні і 2-адресні команди. 3-адресні команди використовуються вкрай рідко, а 4-адресні не використовуються зовсім.

Внаслідок різноманітності форматів команд і даних (числа, символи, структури і т.д.), а також їх розташування сформувались різні способи адресації команд і операндів, які розглянемо нижче.

Способи адресації даних. Безпосередній, прямий, непрямий, реєстровий відносний режими адресації.

Способи адресації даних визначають механізми обчислення ефективних адрес операндів в пам'яті і доступу до операндів. Виділяють наступні способи (режими) адресації / 2, 6 /:

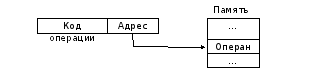

1) безпосередній - дозволяє задавати фіксовані значення операнда безпосередньо в адресній частині команди, тобто, дане є частиною команди (Малюнок 5.1). Такий режим адресації зручний при роботі з константами.

Малюнок 5.1 - Безпосередня адресація

Приклади: mov ax, 5564h

add al, 1101001100b

Слід пам'ятати, що безпосередній операнд може бути заданий тільки як операнд-джерело. Недоліком безпосередньої адресації є необхідність розширення формату команд за рахунок вказівки самого операнда в адресному полі команди.

2) прямий - адреса операнда міститься в коді команди (Малюнок 5.2). Використовується при роботі зі змінними і константами, місце розташування яких в пам'яті не змінюється в процесі виконання завдання.

Малюнок 5.2 - Пряма адресація

Таким чином, в коді команди вказується зміщення операнда в пам'яті.

Приклад: d_s segment

assume ds: d_s, cs: c_s

mov ax , mm ; За адресою mm пересилається 3154h

Після виконання третьої команди в регістрі ax буде записано значення за адресою mm в пам'яті, тобто, число 3154h.

3) регістровий - дане міститься в певному командою регістрі, тобто, в адресному полі команди вказується адреса регістра.

Приклади: mov ax, cx

Реєстрову адресацію легко відрізнити від усіх інших за тією ознакою, що всі операнди команд є регістрами. Такі команди є найбільш компактними і виконуються швидше інших типів команд, оскільки відсутні звернення до пам'яті.

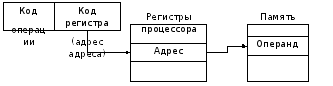

4) регістровий непрямий - є окремим випадком непрямої адресації, коли адреса, що вказується в команді, є покажчиком комірки, що містить зсув операнда в пам'яті (Малюнок 5.3).

Фактично в команді вказується адреса адреси, причому в якості регістру адреси може виступати базовий регістр BP або індексні регістри SI або DI.

Непряма адресація є більш ефективною, ніж пряма, оскільки в адресному полі команди вказується тільки адреса регістра, який коротше повної адреси операнда в пам'яті. Однак при цьому режимі адресації потрібна попередня завантаження регістра непрямим адресою пам'яті, на що витрачається додатковий час.

Приклади: mov ax,

Якщо в регістрі si міститься 10, то в регістр ax буде поміщено значення, що перебуває по зсуві 10 в сегменті даних.

Малюнок 5.3 - Непряма адресація

Непряму адресацію зручно використовувати при вирішенні завдань, коли залишаючи незмінним адреса регістра в команді, можна змінювати вміст комірки з цією адресою.

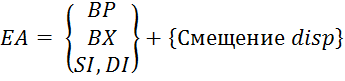

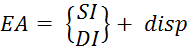

5) регістровий відносний - є узагальненням методів адресації, що забезпечують обчислення ефективної адреси ( EA) Операнда в пам'яті у вигляді суми базового значення адреси і «зміщення» disp, зазначених вище в команді (Малюнок 5.4) і (Формула 5.1).

![]()

Малюнок 5.4 - Формування ефективного адреси при

відносної адресації

(5.1)

(5.1)

Відносну адресацію широко застосовують як для адресації пам'яті, представленої у вигляді блоків (наприклад, сегментів), так і для адресації спеціальних структур даних: масивів, записів та ін. Залежно від способу використання адресується в команді регістра, розрізняють базовий і індексний режими адресації.

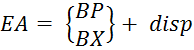

5.1) індексний - застосовується для обробки упорядкованих масивів даних, кожне з яких визначається власним номером. Тоді базова адреса масиву задається зсувом disp, вказуються в команді, а значення індексу (номер елемента масиву) визначається вмістом індексного регістра (Формула 5.2).

(5.2)

(5.2)

Приклад: d_s segment

mas db 3,5,1,8,9, '$'

assume ds: d_s, cs: c_s

mov si, 0; в si-номер елемента масиву

m1: mov ah, mas ; Mas- зміщення

; В ah - значення елемента масиву mas з

; Номером в si

Індексна адресація зручна, якщо необхідно записати або вважати список даних з послідовних комірок пам'яті не підряд, а з деяким кроком, зазначеним в індексі.

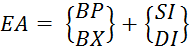

5.2) базовий - застосовується для доступу до структур даних змінної довжини. Тоді базовий адреса, що визначає початок набору елементів, зберігається в базовому регістрі, а зміщення в команді визначає відстань до певного елемента (Формула 5.3).

(5.3)

(5.3)

Цей режим адресації зручно використовувати для записів - структур даних, що містять поля різної довжини і можливо різних типів.

Розглянемо приклад організації записи про співробітників деякого відділу і доступу до неї і її полях. Домовимося, що всі поля символьні.

worker struc; інформація про співробітника

nam db 30 dup ( ""); прізвище, ім'я, по батькові

position db 30 dup ( ""); посада

age db 2 dup ( ''); вік

standing db 2 dup ( ''); стаж

salary db 5 dup ( ''); оклад в рублях

; Опис одного співробітника

sotr1 worker<‘Иванов Пётр Сергеевич’,

'Програміст', '30', '8', '15000'\u003e

assume ds: d_s, cs: c_s

; Завантажуємо в bx адресу початку запису (базовий адреса)

lea bx , sotr 1

; В ax - значення за адресою bx + зсув по полю age

; Тобто., Від початку запису знаходимо осередку,

mov ax , word ptr [ bx ]. age

У записах з полями різної довжини вміст адресується регістра відповідає початку запису, а зміщення в команді - віддалі в запису.

Способи адресації даних. Регістровий, базовий індексний, відносний базовий індексний режими адресації.

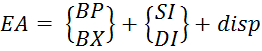

6) Базово- індексний - використовується для доступу до елементів масиву, що адресується покажчиком. Базова адреса масиву задається покажчиком бази (базовим регістром), а номер елемента масиву - вмістом індексного регістра (Формула 5.4).

(5.4)

(5.4)

Приклад: mov ax, bx

Якщо в bx міститься 100, а в si знаходиться 52, то за адресою (зміщення) 152 в сегменті даних знаходиться шукане дане.

Такий режим адресації зручно використовувати при роботі зі складними структурами даних, оскільки дозволяє змінювати дві адресні компоненти.

7) Відносний базовий індексний - використовується для адресації елементів в указуваному масиві записів. Базова адреса масиву задається покажчиком бази, номер запису (тобто, елемента масиву) визначається вмістом індексного регістра, а зміщення в команді вказує відстань до запису (Формула 5.5).

(5.5)

(5.5)

; Опишемо масив з 5 співробітників зі значеннями за

; замовчуванням

mas_sotr worker 5 dup (<>)

assume ds: d_s, cs: c_s

; В bx - адреса початку масиву співробітників

lea bx , mas _ sotr

; В si - зміщення другого запису

mov si , ( type worker )*2

; в ax - стаж другого співробітника

mov ax, .standing

Таким чином, щоб отримати доступ до конкретного поля масиву записів, спочатку необхідно визначити початок масиву, в ньому знайти потрібний запис, а вже в ній - потрібне поле.

Вибір режиму адресації визначається конкретним завданням і в багатьох випадках очевидний. Однак виникають ситуації, коли для звернення до одних і тих же елементів даних допускається використання декількох способів адресації. В кінцевому підсумку, при написанні програми сам користувач здійснює вибір конкретного режиму адресації.

Способи адресації команд.

Залежно від того, в якому сегменті коду знаходиться необхідна команда і явно чи ні вказується її адреса, виділяють наступні режими адресації команд:

1) внутрішньосегментний прямий- ефективний адреса переходу обчислюється як сума поточного вмісту покажчика команд IP і 8- або 16- бітного відносного зсуву. Даний режим допустимо в умовних і безумовних переходах. наприклад,

Якщо вміст регістрів ah і al нерівні (команда jne), То здійснюється перехід до команди з міткою met.

2) межсегментний прямий - в команді вказується пара: сегмент і зсув. Сегмент завантажується в сегментний регістр CS, а зміщення - в регістр IP. Даний режим допусти тільки в командах безумовного переходу. Наприклад, call far ptr quickSort (виклик процедури quickSort, розташованої в іншому сегменті коду).

Таким чином, при прямої адресації в адресному полі команди міститься адреса переходу - адреса, за якою розміщується така виконувана команда.

3) внутрішньосегментний непрямий - зміщення адреси переходу є вміст регістра або комірки пам'яті, зазначені в будь-якому режимі адресації даних, крім безпосереднього. Вміст покажчика команд IP замінюється відповідним вмістом регістра або комірки пам'яті. Даний спосіб допустимо тільки в командах безумовного переходу. Наприклад, jmp (перейти на команду, адреса якої знаходиться в осередку за адресою, вказаною в регістрі bx).

4) міжсегментного непрямий - вміст регістрів CS і IP замінюється вмістом двох суміжних слів пам'яті, адреса яких зазначений в будь-якому режимі адресації даних, крім безпосереднього і реєстрового. Молодше слово завантажується в регістр IP, старше - в регістр CS. Даний режим допустимо тільки в командах безумовного переходу. Наприклад, call far ptr (виклик процедури, розташованої за адресою, зазначеному в регістрі BP плюс ще 4 байта).

Розглянуті способи адресації команд використовуються практично у всіх системах команд, розширюючи або скорочуючи список команд конкретного мікропроцесора.

Як вже зазначалося раніше, однією з важливих характеристик будь-якого процесора є розрядність його внутрішніх регістрів, а також зовнішніх шин адрес і даних. Наприклад, процесор Intel 8086 має 16-розрядну архітектуру і такий же розрядності шину даних. Таким чином, максимальне число, з яким може працювати процесор, становить ![]() . Однак адресна шина процесора Intel 8086 містить 20 ліній, що відповідає адресного простору Мбайт. Для отримання 20-розрядної фізичної адреси осередку пам'яті потрібно скласти початковий адресу сегмента пам'яті, в якому розташовується ця комірка, і зміщення цього осередку щодо початку сегмента (Малюнок 5.5).

. Однак адресна шина процесора Intel 8086 містить 20 ліній, що відповідає адресного простору Мбайт. Для отримання 20-розрядної фізичної адреси осередку пам'яті потрібно скласти початковий адресу сегмента пам'яті, в якому розташовується ця комірка, і зміщення цього осередку щодо початку сегмента (Малюнок 5.5).

Малюнок 5.5 - Формування фізичної адреси осередку пам'яті

Сегментна адреса без 4 молодших бітів (тобто, поділеній на 16), зберігається в одному з сегментних регістрів (SS, DS, CS, ES).

При обчисленні фізичної адреси процесор примножує вміст сегментного регістра на 16 і додає до отриманого 20-розрядному адресою зміщення.

Сучасні 32-розрядні процесори мають 32-розрядну адресну шину, що відповідає адресного простору Гбайта. Однак описаний вище спосіб формування фізичної адреси не дозволяє вийти за межі 1 Мбайта. Для подолання цього обмеження в 32-розрядних процесорах використовуються два режими роботи: реальний і захищений. В реальному режимі процесор функціонує фактично також, як Intel 8086 з підвищеною швидкодією і може звертатися тільки до 1 Мбайту адресного простору. Залишилося пам'ять, навіть якщо вона встановлена на комп'ютері, використовуватися не може. В захищеному режимі також використовуються сегменти і зміщення, але фізичні початкові адреси сегментів витягуються з таблиць сегментних дескрипторів, індексованих за допомогою тих же сегментних регістрів. Кожен сегментний дескриптор займає 8 байт, з яких 4 байта (32 біта) відводяться під сегментна адреса. Такий механізм дозволяє забезпечити повне використання 32-розрядної адресного простору. У 64-розрядних процесорах також застосовується сегментна організація пам'яті і може використовуватися сегментно-сторінкова / 1 / організація пам'яті; під фізичну адресу відводиться 40, 44, 48, 64 розряду. Таким чином, обсяг адресного простору в 64-розрядних мікропроцесорах може становити від 1Тбайта (1 терабайт - байт) до декількох Ебайтов (1 ексабайт - байт).

У попередніх розділах згадувалося про те, що процесор, з одного боку, координує функціонування окремих пристроїв обчислювальної машини, з іншого, - сам виконує обчислення відповідно до програми користувача (принцип програмного управління). Далі розглянемо, яким чином здійснюється виконання команд процесором і його взаємодію з іншими пристроями.

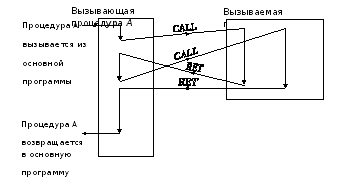

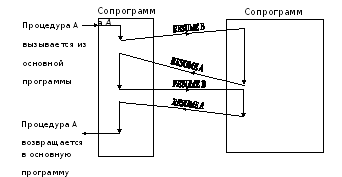

Передача управління. Переходи і процедури.

Згідно / 8 /, потік управління - це послідовність, в якій команди виконуються динамічно (під час виконання програми). Більшість команд не змінюють потік управління: після виконання однієї команди виконується команда, розташована слідом за нею в пам'яті. Лічильник команд (IP) після виконання кожної команди збільшується на число, відповідне довжині команди. Зміна потоку управління відбувається при наявності команд переходів (умовних і безумовного), виклику процедур, співпрограми, а також при виникненні виключень і переривань.

1) команди переходу. При виконанні команд переходу в лічильник команд IP примусово записується нове значення - нова адреса в пам'яті, починаючи з якого будуть виконуватися команди.

команда безумовного переходу забезпечує перехід по заданому адресою без перевірки будь-яких умов. Наприклад, jmp met, означає перехід до команди, яка починається з адреси met в тексті програми. При цьому всі попередні їй команди пропускаються.

умовний перехід (Розгалуження) відбувається тільки при дотриманні певного умови, в іншому випадку виконується наступна по порядку команда програми. Умовою, на підставі якого здійснюється перехід, найчастіше виступають ознаки результату виконання попередньої арифметичної або логічної команди. Кожен з ознак фіксується в своєму розряді регістра прапорів PSW. Можливий і такий підхід, коли рішення про перехід приймається в залежності від стану одного з регістрів загального призначення, куди попередньо поміщається результат операції порівняння / 3 /. Розглянемо приклади:

|

jz m1 m1: add al, 2 |

cmp ah, al je m1 m1: add al, 2 |