Processeurs Intel - comment ils fonctionnent et les principes de base. CPU. Types et différences de processeurs

Il est naturel de considérer les étapes de développement des MP, les réalisations correspondantes, leurs principales caractéristiques architecturales et autres sur la base des MP d'Intel (INTegrated ELectronics). Il existe également un certain nombre de sociétés - AMD (Advanced Micro Devices), Cyrix, Texas Instruments, etc., qui concurrencent plus ou moins avec succès Intel Corporation avec leurs produits.

Les principaux paramètres du MP sont les suivants :

- fréquence d'horloge;

- le degré d'intégration du microcircuit (combien de transistors sont contenus dans la puce);

- la largeur des données internes (le nombre de bits que le MP peut traiter simultanément) ;

- capacité de données externes (le nombre de bits transmis simultanément dans le processus d'échange de données entre la CPU et d'autres éléments);

- mémoire adressable (dépend du nombre de bits d'adresse).

Processeurs Intel

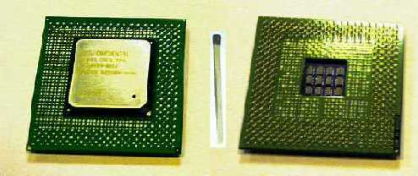

(22 mars 1993). Pentium est  processeur superscalaire avec bus d'adresses 32 bits et bus de données 64 bits, fabriqué en technologie submicronique avec une structure MOS complémentaire, composé de 3,1 millions de transistors (sur une surface de 16,25 cm2). Le processeur comprend les blocs suivants :

processeur superscalaire avec bus d'adresses 32 bits et bus de données 64 bits, fabriqué en technologie submicronique avec une structure MOS complémentaire, composé de 3,1 millions de transistors (sur une surface de 16,25 cm2). Le processeur comprend les blocs suivants :

- Coeur. Le principal appareil exécutif. Les performances du MP à une fréquence d'horloge de 66 MHz sont d'environ 112 millions d'instructions par seconde (MIPS). Par rapport au processeur 80486 DX, les performances ont été multipliées par 5 avec deux pipelines permettant l'exécution simultanée de plusieurs instructions.

- Le prédicteur de branche essaie de deviner la direction de branchement du programme et précharge les informations dans les blocs de prélecture et de décodage.

- Le tampon cible de branche (BTB) fournit une prédiction de branche dynamique. Principe de fonctionnement : « Si la prédiction est correcte, alors l'efficacité augmente, et sinon, le convoyeur doit être complètement abandonné. Selon Intel, la probabilité de prédire correctement les transitions dans les processeurs Pentium est de 75 à 80 %.

- L'unité à virgule flottante effectue un traitement en virgule flottante. Le traitement graphique, les applications multimédias et l'utilisation intensive du PC pour les tâches informatiques nécessitent des performances élevées lors de l'exécution d'opérations en virgule flottante.

- Cache de niveau I. Le processeur dispose de deux banques de mémoire de 8 Ko chacune, la 1ère pour les instructions, la 2ème pour les données plus rapides que les plus volumineuses mémoire externe mémoire cache (cache L2)

- Interface de bus. Transmet un flux de commandes et de données à la CPU, et transfère également les données de la CPU.

Le processeur Pentium a introduit le SMM (System Management Mode). Ce mode permet de mettre en œuvre des fonctions système de très haut niveau, dont la gestion de l'alimentation ou la sécurité, en toute transparence pour l'OS et les applications en cours d'exécution.

Le passage à 60 MHz et plus était une réalisation importante, et les problèmes de refroidissement ont été résolus en conséquence (la surface du processeur chauffe jusqu'à 85 ° C).

(1er novembre 1995). Le Pentium Pro utilise un tampon L2 de 256 Ko (cache) situé dans une puce séparée et monté dans un boîtier CPU pour améliorer les performances. En conséquence, il est devenu possible de décharger efficacement cinq dispositifs exécutifs : deux blocs d'arithmétique d'entiers ; bloc de chargement; bloc d'enregistrement ; FPU (unité à virgule flottante).

Pentium P55 (Pentium MMX), 8 janvier 1997 Pentium MMX - Version Pentium avec caractéristiques supplémentaires... La technologie MMX était censée ajouter/étendre les capacités multimédia des ordinateurs. La technique SIMD (SMD) est mise en œuvre, axée sur les algorithmes et les types de données typiques pour Logiciel multimédia. Le MMX a été annoncé en janvier 1997, cadencé à 166 et 200 MHz, et la version 233 MHz est apparue en juin de la même année. Processus technologique 0,35 microns, 4,5 millions de transistors.

(7 mai 1997). Le processeur est une modification du Pentium Pro avec prise en charge des capacités MMX. Les premiers PII sont annoncés comme des processeurs pour ordinateurs de bureau haut de gamme. La conception du boîtier a été modifiée - la plaquette de silicium avec contacts a été remplacée par une cartouche, la fréquence du bus et la fréquence d'horloge ont été augmentées et les commandes MMX ont été étendues.

Il existe également un modèle pour ordinateurs portables - Pentium II PE et pour postes de travail - Pentium II Heon 450 MHz.

Céleron(15 avril 1998). Celeron est un P2 simplifié pour les ordinateurs bon marché. Les principales différences entre ces processeurs résident dans la taille du cache L2 et la fréquence du bus. Tous ces processeurs sont fabriqués en technologie 0,25 micron et comportent de 7,5 à 19 millions de transistors.

(26 février 1999). P3 est l'un des plus productifs Processeurs Intel, mais dans sa conception, il n'est pas très différent de P2, la fréquence a été augmentée et environ 70 nouvelles commandes ont été ajoutées. En octobre 1999, une version pour ordinateurs portables, fabriqué selon la technologie 0,18 micron avec des fréquences de 400 à 733 MHz. Pour les postes de travail et les serveurs, il y a RZ Heon, axé sur la logique système GX avec un cache L2 de 512 Ko, 1 ou 2 Mo. Le processus technologique est de 0,25 micron, le bus système fonctionne à une fréquence de 100 MHz, il existe une version 0,18 micron avec une fréquence de bus de 133 MHz, ainsi que des modèles pour 600, 666 et 733 MHz.

(Willamette, 2000; Northwood, 2002). Naturellement, tôt ou tard, l'architecture de PIII devait devenir obsolète. Le fait est qu'ayant atteint la fréquence de 1 GHz, Intel a rencontré des problèmes pour augmenter encore la fréquence de ses processeurs : le Pentium III à 1,13 GHz a dû être retiré en raison de son instabilité. Une nouvelle augmentation de la fréquence des processeurs existants entraîne une augmentation toujours plus faible de leurs performances. Le problème est que les latences (retards) qui surviennent lors de l'accès à certains nœuds de processeur sont déjà trop élevées dans P6.

Ainsi, le Pentium IV est né - il est basé sur une architecture appelée architecture Intel NetBurst. Avec ce nom, Intel a tenu à souligner que l'objectif principal du nouveau processeur est d'accélérer l'exécution des tâches de streaming de données directement liées aux technologies Internet et multimédia en plein essor.

L'architecture NetBurst est basée sur plusieurs innovations, ensemble pour atteindre l'objectif ultime de fournir une marge de performance et une évolutivité future pour la famille de processeurs Pentium IV. Les technologies clés comprennent :

- Technologie Hyper Pipelined - Le pipeline Pentium IV comprend 20 étages ;

- Exécution dynamique avancée - prédiction de transition améliorée et exécution dans le désordre ;

- Trace Cache - un cache spécial est utilisé pour mettre en cache les instructions décodées dans le Pentium IV ;

- Moteur d'exécution rapide - L'ALU du Pentium IV fonctionne à deux fois la fréquence du processeur lui-même ;

- SSE2 - ensemble étendu de commandes pour le traitement des données en continu ;

- Le bus système 400 MHz est un nouveau bus système.

Pentium IV Prescott(février 2004). Début février 2004, Intel a annoncé quatre nouveaux processeurs Pentium IV (2,8, 3,0, 3,2 et 3,4 GHz) basés sur le noyau Prescott, qui comprend un certain nombre d'innovations. Parallèlement à la sortie de quatre nouveaux processeurs, Intel a présenté le processeur Pentium IV 3.4 EE (Extreme Edition) basé sur le noyau Northwood et doté de 2 Mo de cache L3, ainsi qu'une version simplifiée du Pentium IV 2.8 A basée sur le Prescott noyau avec une fréquence de bus limitée ( 533 MHz).

Les nouveaux processeurs ont le même design que ceux basés sur le noyau Northwood, donc, pour les distinguer, Intel a introduit un nouvel indice dans le nom du processeur - E. Par exemple, le processeur Pentium IV 3.2 C est basé sur le noyau Northwood , prend en charge le bus 800 MHz et la technologie HT, tandis que le Pentium IV 3.2 E est basé sur le noyau Prescott et prend également en charge le bus 800 MHz et la technologie HT.

Prescott est fabriqué à l'aide de la technologie 90 nm, ce qui a permis de réduire la surface du cristal lui-même, tandis que le nombre total de transistors a plus que doublé. Alors que le noyau Northwood mesure 145 mm2 et contient 55 millions de transistors, le noyau Prescott mesure 122 mm2 et contient 125 millions de transistors.

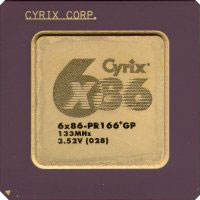

Processeurs Cyrix

Dévoilé en octobre 1995, 6x86 était  le premier processeur compatible Pentium pour permettre la pénétration du marché et la collaboration avec la division IBM Microelectronics. L'adoption du 6x86 a d'abord été lente car Cyrix fixait des prix trop élevés, pensant à tort que puisque l'efficacité du processeur était comparable à celle d'Intel, son prix pourrait être le même. Dès que Cyrix a redéfini sa position, la puce a commencé à exercer une influence significative sur sa part de marché en tant qu'alternative haute performance à la série Pentium.

le premier processeur compatible Pentium pour permettre la pénétration du marché et la collaboration avec la division IBM Microelectronics. L'adoption du 6x86 a d'abord été lente car Cyrix fixait des prix trop élevés, pensant à tort que puisque l'efficacité du processeur était comparable à celle d'Intel, son prix pourrait être le même. Dès que Cyrix a redéfini sa position, la puce a commencé à exercer une influence significative sur sa part de marché en tant qu'alternative haute performance à la série Pentium.

À partir du 6x86, les processeurs Cyrix étaient capables de niveaux de performances équivalents à la puce Pentium, mais à une fréquence inférieure. Le Processor Performance Rating - P-rating est utilisé pour évaluer les performances (la désignation P100 +, par exemple, symbolise les performances équivalentes à un Pentium avec une fréquence de 100 MHz). Les processeurs Cyrix (comme AMD) fonctionnent traditionnellement à des fréquences inférieures à la valeur numérique de leur P-rating, sans dégradation notable des performances. Par exemple, P133 + (P-rating) fonctionne à 110 MHz, tandis que P150 + et P166 + fonctionnent respectivement à 120 et 133 MHz.

La supériorité du 6x86 provenait des améliorations de l'architecture de la puce, qui ont permis au 6x86 d'accéder à son cache interne et de s'enregistrer en un cycle d'horloge (le Pentium utilise généralement deux cycles ou plus pour accéder au cache). De plus, le cache principal 6x86 a été fusionné, plutôt que d'inclure deux sections 8K distinctes pour les instructions et les données. Ce modèle combiné était capable de stocker des instructions et des données à tous égards, offrant un taux de réussite du cache de 90 %. Le processeur contient 3,5 millions de transistors, fabriqués à l'origine avec une technologie à cinq couches de 0,5 micron. Interface - Socket 7. Tension de base - 3,3 V. Les caractéristiques du 6x86 sont similaires à celles du Pentium. Cependant, il inclut également de nouvelles fonctionnalités : suppression des dépendances de données, prédiction de branchement et exécution d'instructions dans le désordre (la possibilité pour des instructions plus rapides de quitter la file d'attente du pipeline sans perturber le processus d'exécution du programme). Tout cela augmente le niveau de performance du 6x86, contrairement au Pentium avec la même fréquence.

Cependant, les processeurs 6x86 étaient confrontés à de nombreux problèmes, notamment une surchauffe, de mauvaises performances en virgule flottante et une incompatibilité avec Windows NT. Cela a nui au succès du processeur, et la concurrence avec le Pentium a été de courte durée et s'est terminée avec le lancement de l'Intel Pentium MMX.

Cyrix MediaGX... L'introduction du processeur MediaGX en février 1997 a défini la première nouvelle architecture de PC en une décennie et a défini un nouveau segment de marché - le "PC de base" à faible coût. La croissance de ce marché a été explosive et la technologie des processeurs Cyrix et l'innovation au niveau du système ont été un élément clé.

Plus le nombre de processus traités directement sur le processeur central du PC est élevé, plus les performances globales du système sont élevées. Dans les conceptions informatiques traditionnelles, l'unité centrale de traitement traite les données à une fréquence en mégahertz, tandis que le bus qui déplace les données vers et depuis d'autres composants ne fonctionne qu'à la moitié de la vitesse ou moins. Cela signifie qu'il faut plus de temps pour que les données se déplacent vers (et depuis) le processeur. Cyrix a supprimé ce goulot d'étranglement avec l'introduction de la technologie MediaGX. L'architecture MediaGX intègre les graphiques, l'audio, le PCI et le gestionnaire de mémoire dans un bloc processeur, éliminant ainsi les conflits potentiels du système et les problèmes de configuration de l'utilisateur final. Il se compose de deux puces - le processeur MediaGX et le coprocesseur MediaGX Cx5510. Le processeur utilise un socket spécial qui nécessite une carte mère spécialement conçue. MediaGX est un processeur compatible x86 qui connecte directement le bus PCI et la DRAM EDO via un bus de données dédié 64 bits. Cyrix affirme que la technique de compression utilisée sur le bus de données élimine le besoin de cache L2. Il y a un cache L1 combiné (16 Ko) sur le processeur central - de la même taille que sur une puce Pentium standard. Les graphiques sont traités directement par un pipeline spécial sur le processeur et le contrôleur de moniteur se trouve également sur le processeur principal. Il n'y a pas de mémoire vidéo, pas de mémoire tampon d'images stockée dans la mémoire principale (architecture traditionnelle de mémoire unifiée - UMA), à la place, il utilise sa propre technologie de compression d'affichage Cyrix (DCT). Les données VGA sont gérées par le matériel informatique, mais les registres VGA sont contrôlés par les programmes Cyrix - Virtual System Architecture (VSA). La puce compagnon MediaGX Cx5510 contient un contrôleur audio et utilise également le logiciel VSA pour émuler les capacités des cartes son standard. Cette puce connecte le processeur MediaGX via le bus PCI au bus ISA, ainsi qu'aux ports IDE et I/O, c'est-à-dire qu'elle remplit les fonctions traditionnelles d'un chipset.

La réponse de Cyrix à Technologie Intel MMX était 6x86MX, lancé à la mi-1997, peu de temps avant l'acquisition de la société par National Semiconductor. L'entreprise est restée fidèle au format Socket 7 pour sa nouvelle puce, qui a maintenu les coûts des fabricants de systèmes et, finalement, des consommateurs au niveau requis, prolongeant la durée de vie de la puce et des cartes mères existantes.

L'architecture de la nouvelle puce est restée essentiellement la même que celle de son prédécesseur, avec l'ajout d'instructions MMX, quelques améliorations au Floating Point Unit, un grand cache universel (64 Ko) de premier niveau et une unité de gestion de mémoire étendue.

Le processeur 6x86MX a été bien reçu sur le marché, car le 6x86MX / PR233 (cadencé à 187 MHz) était plus rapide que le Pentium II (233 MHz) et AMD KB. Le MX a également été le premier processeur phare à pouvoir fonctionner sur un bus frontal de 75 MHz, offrant des avantages évidents en matière de bande passante et des performances globales accrues. Cependant, le 6x86MX fonctionnait en virgule flottante bien moins bien que ses concurrents, ce qui affectait négativement le traitement des graphiques 3D.

Cyrix MII... Le processeur МII est un développement du 6x86МХ fonctionnant à des fréquences plus élevées. À l'été 1998, les processeurs de 0,25 micron MII-300 et MII-333 étaient fabriqués dans les nouvelles installations de production de National Semiconductor en pcs. Le Maine visait à développer la technologie 0,22 micron, se dirigeant vers son objectif ultime de 0,18 micron en 1999.

Processeurs AMD

Micro-appareils avancés de longue date,  comme Cyrix, il a produit les unités centrales de traitement 286, 386 et 486 basées sur des conceptions Intel. Le K5 était le premier processeur x86 construit de manière indépendante pour lequel AMD avait de grands espoirs. Cependant, le rachat par AMD d'un concurrent californien au printemps 1996 semble avoir créé une opportunité de mieux préparer sa prochaine attaque contre Intel. Le K6 a commencé sa vie sous le nom de Nx686, renommé après l'acquisition de NextGen. La série KB de processeurs compatibles MMX a été lancée à la mi-1997, quelques semaines avant le Cyrix 6x86MX, et a immédiatement été saluée par la critique.

comme Cyrix, il a produit les unités centrales de traitement 286, 386 et 486 basées sur des conceptions Intel. Le K5 était le premier processeur x86 construit de manière indépendante pour lequel AMD avait de grands espoirs. Cependant, le rachat par AMD d'un concurrent californien au printemps 1996 semble avoir créé une opportunité de mieux préparer sa prochaine attaque contre Intel. Le K6 a commencé sa vie sous le nom de Nx686, renommé après l'acquisition de NextGen. La série KB de processeurs compatibles MMX a été lancée à la mi-1997, quelques semaines avant le Cyrix 6x86MX, et a immédiatement été saluée par la critique.

Le K6 était presque 20 % plus petit que le Pentium Pro et contenait en même temps 3,3 millions de transistors de plus (8,8 contre 5,5 millions). Le processeur K6 prend en charge la technologie MMX d'Intel, y compris 57 nouvelles instructions x86 conçues pour le développement de logiciels multimédias. Le niveau de performance du K6 est très similaire au Pentium Pro des fréquences correspondantes avec son cache L2 maximum de 512 Ko. La similitude avec la puce Cyrix MX (mais dans une moindre mesure) - opération en virgule flottante - était une zone de faiblesse relative par rapport au Pentium Pro ou Pentium II.

AMD K6-2... Les processeurs AMD K6-2 avec 9,3 millions de transistors ont été fabriqués en utilisant la technologie AMD 0,25 micron. Le processeur était conditionné dans un boîtier CPGA (Ceramic Pin Grid Array) compatible Super7 à 100 MHz. Le K6-2 comprend la microarchitecture R1SC86 innovante et efficace, un grand cache L1 de 64 Ko (cache de données à double port 32 Ko, cache d'instructions de 32 Ko avec cache de pré-déchiffrement de 20 Ko en option) et un module à virgule flottante amélioré.

Ses performances effectives étaient estimées à 300 MHz lors de son lancement à la mi-1998, et au début de 1999, le processeur le plus rapide disponible était la version 450 MHz. Les capacités 3D du K6-2 étaient différentes. réalisation importante... Elles ont été incorporées dans la technologie AMD 3DNow!, sous la forme d'un nouvel ensemble de 21 instructions complétant les instructions MMX standard déjà incluses dans l'architecture KB, ce qui a accéléré le traitement des applications 3D. Annoncé début 2001, le processeur K6-2 (550 MHz) devait être le processeur le plus rapide et le dernier d'AMD pour le facteur de forme Socket 7 vieillissant, remplacé plus tard par le processeur Duron sur le marché prometteur des ordinateurs de bureau.

AMD K6-III... En février 1999, AMD annonce le lancement d'un lot de processeurs AMD K6-III 400 MHz, nom de code narptooth, et teste la version 450 MHz. Caractéristique clé Ce nouveau processeur était un développement innovant - Cache à trois niveaux.

Traditionnellement, les processeurs PC utilisent deux niveaux de cache :

- le cache de premier niveau (L1), qui est généralement situé sur la puce ;

- un cache de deuxième niveau (L2) qui peut être situé hors du processeur, sur la carte mère ou le slot, ou directement sur la puce du processeur.

Une règle générale lors de la conception d'un sous-système de cache est que plus le cache est grand et rapide, meilleures sont les performances (le cœur du processeur peut accéder aux instructions et aux données plus rapidement).

Reconnaissant les avantages d'un cache large et rapide pour répondre aux demandes d'applications de performances PC de plus en plus exigeantes, le cache à trois niveaux d'AMD a introduit des innovations architecturales de cache conçues pour améliorer les performances sur les PC basés sur Super7 :

- Cache K2 interne (256 Ko) fonctionnant à pleine vitesse du processeur AMD-K6-III et complétant le cache L1 de 64 Ko qui était standard dans la famille de processeurs AMD-K6 ;

- cache interne multiport, permettant la lecture et l'écriture simultanées de 64 bits dans les caches L1 et L2 ;

- bus de processeur principal (100 MHz), fournissant une connexion à la mémoire cache résidente sur carte mère extensible de 512 à 2048 Ko.

La conception du cache interne multiport du processeur AMD-K6-III a permis à la fois au cache L1 (64 Ko) et au cache L2 (256 Ko) d'effectuer simultanément des opérations de lecture et d'écriture 64 bits par cycle de processeur. En plus de cette conception de cache multiport, le cœur du processeur AMD-K6-III était capable d'accéder simultanément aux caches L1 et L2, augmentant ainsi la bande passante globale du processeur.

AMD a affirmé qu'avec un cache L3 entièrement réglé, le K6-III avait un avantage de taille de cache de 435% par rapport au Pentium III et donc un avantage significatif en termes de performances. En fin de compte, cependant, il était destiné à vivre une vie relativement courte dans le domaine des ordinateurs de bureau, étant poussé à l'arrière-plan par le processeur AMD Athlon plus efficace quelques mois plus tard.

Sortie Processeur Athlon l'été 1999 a été le coup le plus réussi d'AMD. Cela les a rendus fiers de ce qu'ils ont produit  le premier processeur de septième génération (il présentait suffisamment de différences architecturales radicales par rapport aux Pentium II / III et K6-III pour mériter le nom de processeur de prochaine génération), et cela signifiait également qu'ils arrachaient le leadership technologique à Intel.

le premier processeur de septième génération (il présentait suffisamment de différences architecturales radicales par rapport aux Pentium II / III et K6-III pour mériter le nom de processeur de prochaine génération), et cela signifiait également qu'ils arrachaient le leadership technologique à Intel.

Le mot grec ancien Athlon signifie trophée ou jeux. L'Athlon est le processeur avec lequel AMD espérait accroître sa réelle présence concurrentielle dans le secteur des entreprises, au-delà de son avantage traditionnel sur les marchés des jeux grand public et 3D. Le noyau est placé sur une puce de 102 mm2 et contient environ 22 millions de transistors.

Duron.À la mi-2000, le processeur Duron est sorti pour la maison et le bureau. Le nom vient du latin "durare" - "éternel", "à long terme". Les mémoires cache L1 (128 Ko) et L2 (64 Ko) sont situées sur la carte. Le bus système principal fonctionne à 200 MHz. Technologie 3DNow! améliorée prise en charge Technologie 0,18 micron, fréquences 600, 650 et 700 MHz. Interface - Prise A 462 broches.

Athlon 64.À l'automne 2003, deux  Modèles de processeurs AMD - Athlon 64 pour le grand public et Athlon 64 FX-51 pour le multimédia et candidatures professionnelles(architecture K8). Dans le système de notation AMD Athlon 64 a une fréquence équivalente de 3200+, avec une fréquence physique de 2 GHz, FX-51 est légèrement plus élevée - 2,2 GHz. Une innovation architecturale importante est l'intégration du concentrateur de contrôleur de mémoire système (MCH) directement dans le processeur. Cela signifie que la carte mère (plus précisément, le chipset) ne devrait plus contenir de puce de contrôleur Northbridge distincte. Il supprime également le besoin d'un bus système principal (FSB), ainsi que toutes les latences qu'il introduit. Au lieu de cela, le K8 utilise HyperTransport (jusqu'à 6,4 Go / s de bus système) pour se connecter à Southbridge, aux contrôleurs AGP ou à d'autres processeurs. Cela permet à la mémoire de fonctionner à pleine fréquence du processeur, réduit la latence (latence) et améliore l'efficacité de la mémoire. Le processeur convient aux applications 32 et 64 bits.

Modèles de processeurs AMD - Athlon 64 pour le grand public et Athlon 64 FX-51 pour le multimédia et candidatures professionnelles(architecture K8). Dans le système de notation AMD Athlon 64 a une fréquence équivalente de 3200+, avec une fréquence physique de 2 GHz, FX-51 est légèrement plus élevée - 2,2 GHz. Une innovation architecturale importante est l'intégration du concentrateur de contrôleur de mémoire système (MCH) directement dans le processeur. Cela signifie que la carte mère (plus précisément, le chipset) ne devrait plus contenir de puce de contrôleur Northbridge distincte. Il supprime également le besoin d'un bus système principal (FSB), ainsi que toutes les latences qu'il introduit. Au lieu de cela, le K8 utilise HyperTransport (jusqu'à 6,4 Go / s de bus système) pour se connecter à Southbridge, aux contrôleurs AGP ou à d'autres processeurs. Cela permet à la mémoire de fonctionner à pleine fréquence du processeur, réduit la latence (latence) et améliore l'efficacité de la mémoire. Le processeur convient aux applications 32 et 64 bits.

En même temps qu'AMD annonçait l'Athlon 64, Microsoft annonçait une version bêta de Windows XP 64-Bit Edition pour les processeurs 64 bits, qui peut naturellement fonctionner sur les deux Processeurs AMD Athlon 64 (PC) et AMD Opteron (postes de travail).

Travailler avec la liste de prix

Lors du choix d'un microprocesseur, il est nécessaire de prendre en compte certaines caractéristiques, par exemple

- Processeurs Intel.

- Processeurs AMD et Cyrix.

- Versions modernes des processeurs Intel et AMD (contrairement aux plus anciens).

- Fabricants alternatifs de microprocesseurs.

- Décrire les composants de la liste de prix

- AMD ATHLON-64 X2 6000+ BOX (ADV6000) 1Mb / 2000MHz Socket AM2

- AMD ATHLON-64 2800+ (ADA2800) 512K / 800MHz Socket-754

- Intel Core 2 Duo E6550 2,33 GHz / 4 Mo / 1333 MHz 775-LGA

- Intel Pentium 4 1.5GHz / 256K / 400MHz 423-PGA

Le processeur remplit les fonctions suivantes :

1) calculer les adresses des commandes et des opérandes ;

2) récupérer et décoder les commandes de la RAM ;

3) récupérer les données de la RAM, de la mémoire du microprocesseur et des registres des adaptateurs d'appareils externes ;

4) recevoir et traiter des demandes et des commandes provenant d'appareils externes ;

5) traitement et enregistrement des données dans la RAM, les registres de microprocesseur et les registres d'adaptateurs de périphériques externes ;

6) génération de signaux de commande pour tous les autres nœuds et blocs de l'ordinateur ;

7) passez à la commande suivante.

Selon / 4 /, les principaux paramètres des microprocesseurs sont : mordant, fréquence d'horloge de fonctionnement, taille du cache, composition d'instructions, constructif.

1) Profondeur de bits des registres internes- le nombre de bits que le processeur est capable de traiter à la fois. Largeur du bus de données détermine le nombre de bits sur lesquels des opérations peuvent être effectuées simultanément. Largeur du bus d'adresses détermine la quantité de mémoire (espace d'adressage) avec laquelle le processeur peut travailler. Espace d'adressage C'est le nombre maximum de cellules mémoire qui peuvent être directement adressées par le microprocesseur.

2) Fréquence d'horloge de travail (MHz) détermine en grande partie la vitesse du processeur, puisque chaque commande est exécutée dans un certain nombre de cycles d'horloge. Plus le cycle d'horloge de la machine est court, plus les performances du processeur sont élevées. La vitesse de l'ordinateur dépend également de la fréquence d'horloge du bus de la carte système avec lequel le processeur fonctionne.

3) Mémoire cache installé sur la carte microprocesseur a deux niveaux :

3.1) L 1 - mémoire du premier niveau, située à l'intérieur du microcircuit principal (noyau) du processeur et fonctionnant toujours à la pleine fréquence du processeur (apparu pour la première fois dans les microprocesseurs Intel 386SLC et 486).

3.2) L 2 - mémoire de second niveau, un cristal situé sur la carte du microprocesseur et connecté au coeur par un bus interne (introduit pour la première fois dans les microprocesseurs Pentium II). Cette mémoire peut fonctionner à pleine ou à mi-fréquence du processeur.

4) Composition des instructions- liste, type et type de commandes exécutées automatiquement par le microprocesseur. Spécifie directement les procédures qui peuvent être exécutées sur les données et les catégories de données sur lesquelles ces procédures peuvent être exécutées. Un changement significatif dans la composition des instructions s'est produit dans les microprocesseurs Intel 80386 (cette composition est considérée comme la composition de base), Pentium MMX, Pentium III, Pentium 4.

5) Constructif fait référence aux connecteurs physiques dans lesquels le microprocesseur est installé. Différents connecteurs ont une conception différente (connecteur à fente - Slot, connecteur-prise - Soket), un nombre de contacts différent.

Les processeurs sont classés selon différents critères. Conformément à / 4, 13 /, les principales caractéristiques suivantes peuvent être distinguées :

1) Par rendez-vous les microprocesseurs sont divisés en universel et spécialisé... Les premiers sont conçus pour résoudre un large éventail de problèmes ; l'universalité algorithmique est incorporée dans le système de commande. Ainsi, les performances du processeur dépendent faiblement des spécificités des tâches à résoudre. Les processeurs spécialisés sont conçus pour résoudre un certain nombre de tâches ou même une seule tâche, ils ont un ensemble limité d'instructions. Parmi eux se démarquer processeurs de données, processeurs mathématiques et microcontrôleurs.

2) Par le nombre de programmes en cours d'exécution les processeurs sont classés en programme unique(le passage à l'exécution du programme suivant n'a lieu qu'après la fin du programme en cours) et multi-programme(plusieurs programmes fonctionnent en même temps).

3) Par de construction la fonction se distingue par des microprocesseurs bit fixe(ont une capacité en bits strictement définie) et des microprocesseurs avec une profondeur de bits incrémentielle(autoriser les sections à augmenter le nombre de chiffres).

4) Par le nombre de LSI (VLSI) dans l'ensemble de microprocesseurs peut être distingué puce unique, multipuce et sectionnel multipuce processeurs. Dans le premier cas, toutes les parties matérielles du processeur sont implémentées comme un seul LSI (VLSI) ; les capacités de ces processeurs sont limitées par les ressources du cristal et du boîtier. Les processeurs multipuces sont obtenus en divisant la structure logique du processeur en parties fonctionnellement complètes, dont chacune est implémentée sous la forme d'un LSI ou d'un VLSI. Dans ce dernier cas, les parties fonctionnellement complètes de la structure logique du processeur sont divisées en sections, qui sont mises en œuvre sous la forme d'un LSI.

5) Par bitness des informations traitées les microprocesseurs peuvent être 4, 8, 12, 16, 24, 32 et 64 bits. En pratique, les processeurs 32 bits sont les plus courants ; Les processeurs 64 bits sont de plus en plus utilisés.

6) Par type Technologie de fabrication LSI (VLSI) les microprocesseurs sont divisés en deux groupes : les processeurs basés sur des LSI fabriqués selon technologie unipolaire, et les processeurs basés sur LSI fabriqués par technologie bipolaire... Représentants du premier groupe : p-canaliser (p-MOS), m-canaliser (m-MOS), gratuit (CMOS) BIS. (MOS - Conducteur d'oxyde métallique). Le deuxième groupe comprend les LSI basés sur logique transistor-transistor (TTL), logique à couplage d'émetteur (ECL) et logique d'injection intégrale (ET 2 L)... Le type de technologie de fabrication LSI détermine en grande partie le degré d'intégration des microcircuits, la vitesse, la consommation électrique, l'immunité au bruit et le coût des processeurs. Par la complexité de ces caractéristiques, on peut privilégier les microprocesseurs réalisés à l'aide des technologies n-MOS et CMOS, qui offrent une densité de compactage élevée, une vitesse élevée et un coût relativement faible. ESL offre les performances de processeur les plus rapides, mais une faible densité d'emballage et une consommation d'énergie élevée. La technologie I 2 L donne les caractéristiques moyennes des microprocesseurs.

7) Par la nature du système de commande allouer processeurs de jeux d'instructions complets ou SCRC-processeurs(Commande de jeu d'instructions complexe), processeurs à jeux d'instructions réduits ou RISC-processeurs(Commande d'ensemble d'instructions réduite), traitement de texte ultra-large ou VLIW-processeurs(Très long mot d'instruction). Les processeurs CISC ont un grand nombre d'instructions multi-formats, ce qui permet d'utiliser des algorithmes efficaces pour résoudre des problèmes, mais en même temps complique le circuit du processeur et, en général, n'offre pas des performances maximales. L'architecture CISC est inhérente aux processeurs classiques. Les processeurs RISC contiennent un ensemble d'instructions simples que l'on trouve le plus souvent dans les programmes. S'il est nécessaire d'exécuter des commandes plus complexes dans le microprocesseur, elles sont automatiquement assemblées à partir de commandes simples. Tout commandes simples sont de la même taille et prennent un cycle machine à exécuter (l'instruction CISC la plus courte prend généralement quatre cycles à exécuter). Les processeurs RISC 64 bits modernes sont produits par de nombreuses entreprises : Apple (PowerPC), IBM (PPC) etc. Dans les processeurs VLIW, une instruction contient plusieurs opérations qui doivent être exécutées en parallèle. La tâche de répartition du travail entre plusieurs appareils informatiques du processeur est résolue lors de la compilation du programme. Cette approche a permis de réduire la taille des processeurs et la consommation d'énergie. Des exemples de processeurs VLIW sont l'Itanium d'Intel, le McKinley de Hewlett-Packard et d'autres.

8) Par le nombre et le mode d'utilisation des registres internes distinguer rechargeable, multi-batterie et empiler processeurs. Processeurs de batterie Sont des processeurs avec un seul registre de résultat. Leur caractéristique distinctive est la relative simplicité de la mise en œuvre matérielle, ainsi que le format de commande simplifié (sera discuté dans la prochaine leçon). Dans les commandes, l'adresse de l'opérande dans l'accumulateur n'est pas indiquée, et seul le deuxième opérande est adressé. Les inconvénients de tels processeurs sont la nécessité de précharger l'opérande dans l'accumulateur avant d'effectuer l'opération et l'impossibilité d'écrire directement le résultat de l'exécution de la commande dans une cellule mémoire ou un registre arbitraire. V multi-batterie registres, qui constituent la majorité des processeurs modernes, la fonction des registres de résultats peut être assurée par n'importe quel registre ou cellule mémoire à usage général. Dans les commandes, les deux opérandes sont spécifiés explicitement, et le résultat d'une opération est le plus souvent placé à la place de l'un des opérandes. V empiler les processeurs utilisent généralement une grande pile matérielle et une pile externe supplémentaire en mémoire (en cas de manque de matériel). En raison de la disposition spéciale des opérandes dans la pile, le traitement de l'information peut être effectué par des instructions non adressées, ce qui améliore les performances du processeur et économise de la mémoire. De telles instructions extraient un ou deux opérandes de la pile, effectuent une opération arithmétique ou logique appropriée dessus et poussent le résultat vers le haut de la pile. L'inconvénient est la nécessité d'une préparation préalable des données à l'aide de commandes d'adresse.

L'histoire du développement des processeurs et de leurs caractéristiques comparatives peut être trouvée plus en détail dans / 4, 13 /. Examinons ensuite la structure physique et fonctionnelle du processeur.

Organisation physique et fonctionnelle du CPU (par exemple, CPU Intelligence 8086). SHI.

La structure physique du processeur est assez complexe. Conformément à / 4 /, le cœur du processeur contient les principaux modules de commande et d'exécution - des unités permettant d'effectuer des opérations sur des données entières. Les circuits de contrôle locaux comprennent : un bloc à virgule flottante, un module de prédiction de branchement, des registres de mémoire de microprocesseur, des registres de cache de niveau 1, une interface de bus et bien plus encore.

Remarque : Le noyau logique est compris comme le schéma selon lequel le processeur est fabriqué. Physiquement, le noyau est un cristal sur lequel le schéma électrique du processeur est implémenté à l'aide d'éléments logiques.

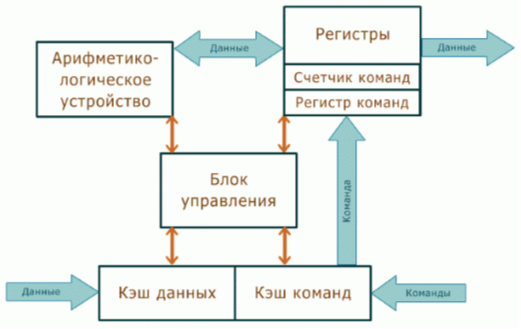

Dans le cas le plus général, la structure fonctionnelle du processeur peut être représentée comme une composition, selon une source / 4, 5 /, en deux parties : appareil de commande (OU) et interface de bus (SHI), selon d'autres / 2 /, - trois blocs : unité opérant (À PROPOS), Unité de contrôle (UB) et bloc d'interface (IB). Les écarts insignifiants existants dans le nombre et le nom des blocs ne violent en aucun cas le nombre et les principes de fonctionnement des composants du processeur. Par conséquent, nous considérerons la première option (plus visuelle) de la source / 4 /.

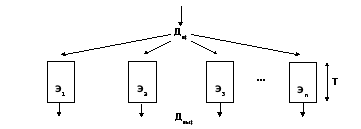

Une structure de processeur typique simplifiée est illustrée à la figure 4.1.

OU contient une unité de contrôle (UU), une unité arithmétique et logique (ALU), un registre d'indicateurs, des registres à usage général (RON), des registres de pointeurs, des registres d'index. SHI contient des registres d'adresses, un bloc de registres (tampon) de commandes, une unité de génération d'adresses, des circuits de contrôle de bus et de ports. Les deux parties du microprocesseur fonctionnent en parallèle et le SHI fonctionne plus rapidement que l'ampli-op. Examinons de plus près ces blocs de processeur.

SHI est destiné à la communication et à la coordination du microprocesseur avec le bus système de l'ordinateur, ainsi qu'à la réception, à l'analyse préliminaire des commandes du programme en cours d'exécution et à la formation des adresses complètes des opérandes et des commandes.

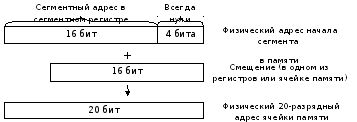

Segmentaire(adresse) s'inscrit avec nœud de la formation de l'adresse implémenter la segmentation de la mémoire. Les commandes et les données sont stockées dans des cellules, et leur emplacement en mémoire est déterminé par les adresses des cellules correspondantes. Étant donné que les instructions et les données au niveau du code sont indiscernables les unes des autres, pour distinguer les instructions et les données, elles sont placées dans différentes zones de mémoire - segments. Segment est une zone de mémoire rectangulaire, caractérisée par une adresse de début et une longueur. Adresse de début (adresse de début de segment) Numéro (adresse) de la cellule mémoire à partir de laquelle le segment commence. Longueur des segments – c'est le nombre de cellules mémoire qu'il contient. Les segments peuvent être de différentes longueurs. Toutes les cellules situées à l'intérieur du segment sont renumérotées à partir de zéro. Les cellules d'un segment sont adressées par rapport au début du segment ; l'adresse de la cellule dans le segment est appelée déplacement ou adresse effective -EA(par rapport à l'adresse de début du segment). Le segment actuel peut être spécifié en chargeant le registre de segment approprié :

1) CS (Code Segment) - définit le début du segment de code courant, dans lequel se trouvent les commandes du programme. La commande est récupérée en utilisant le contenu du registre comme adresse effective IP (Instruction Aiguille) , et comme adresse de segment - le contenu de CS. C'est le registre IP qui stocke l'offset de l'adresse de la commande de programme en cours.

2) DS (Données Segment) - définit le début du segment de données actuel. Les références aux données (à quelques exceptions près) sont faites par rapport au contenu de ce registre.

3) SS (Empiler Segment) - définit le début du segment courant de la pile. Typiquement, toutes les adresses de données associées à la pile sont relatives au contenu de ce registre.

4) ES (Élargi Segment) - définit le début du segment courant supplémentaire, qui est généralement considéré comme un segment de données auxiliaire (pour les transferts inter-segments).

Nœud de génération d'adresses et registre de commandes fonctionnellement font partie de l'UU et ont été discutés ci-dessus.

Lors de l'adressage des périphériques d'entrée-sortie (IO), les registres de segment ne sont pas utilisés. Le processeur interagit avec eux via un espace d'adressage spécial - les ports. Chaque port a un numéro qui correspond à l'adresse de l'appareil qui lui est connecté. Le port de l'appareil correspond à l'équipement d'interface et à deux registres - pour l'échange de données et d'informations de contrôle. Circuit de contrôle de bus et de port remplit les fonctions suivantes :

1) formation de l'adresse du port et des informations de contrôle correspondantes ;

2) recevoir des informations de contrôle du port, des informations sur l'état de préparation du port et son état ;

3) organisation d'un canal de bout en bout dans l'interface système pour la transmission de données entre le port I/O et le processeur.

Le schéma de contrôle des bus et des ports utilise le bus système pour communiquer avec les ports : le bus d'adresses, le bus de données et le bus d'instructions.

Organisation physique et fonctionnelle du processeur (par exemple, processeur Intel 8086). OU.

En général, l'unité d'organisation effectue les opérations spécifiées par les commandes et génère des adresses effectives.

Euh génère des signaux de contrôle à tous les blocs de l'ordinateur. Les blocs fonctionnels suivants peuvent être distingués dans le cadre de la CU :

1) registre de commandes- un registre de stockage qui stocke le code de commande : le code opération et les adresses des opérandes (situé dans la partie interface du processeur) ;

2) décodeur d'opération- un bloc logique qui, conformément au code opération issu du registre de commandes, sélectionne l'une des nombreuses sorties dont il dispose ;

3) micrologiciel de la mémoire morte (ROM) stocke des impulsions de commande pour effectuer des procédures de traitement de l'information dans les blocs de l'ordinateur ; une impulsion à travers le fil sélectionné par le décodeur de fonctionnement lit la séquence requise de signaux de commande à partir de la ROM du micrologiciel ;

4) nœud de génération d'adresses(situé dans le SHI) - un dispositif de calcul de l'adresse complète d'une cellule mémoire (registre) en fonction des détails provenant de la mémoire du microprocesseur ou du registre de commande ;

5) bus de code de données, d'adresses et d'instructions- une partie du bus d'interface interne du processeur.

Ainsi, l'unité de commande génère des signaux de commande pour que le processeur exécute ses fonctions décrites ci-dessus.

Figure 4.1 - Structure de processeur typique simplifiée

ALU est destiné à effectuer des opérations arithmétiques et logiques de transformation de l'information. Fonctionnellement, dans sa forme la plus simple, l'ALU se compose des éléments suivants :

1) additionneur effectue la procédure d'ajout de codes binaires, a une longueur de mot double (32 bits);

2) registres- des cellules mémoires rapides de différentes longueurs : le registre 1 a 32 bits, le registre 2 - 16 bits ; lors de l'addition, le premier terme est placé dans le registre 1, puis le résultat, dans le registre 2 - le deuxième terme ;

3) schéma de contrôle reçoit des signaux de commande de l'unité de commande via les bus de code d'instructions et les convertit en signaux pour commander le fonctionnement des registres et de l'additionneur.

ALU effectue des opérations arithmétiques uniquement sur nombres binaires un point fixe. Pour traiter les nombres à virgule flottante, un coprocesseur mathématique ou des programmes spécialement conçus sont utilisés.

Des informations plus détaillées sur la structure et le fonctionnement du dispositif de commande et de l'ALU peuvent être trouvées dans / 3 - 5 /.

Registres d'ampli-op- une partie de la mémoire du microprocesseur. Regardons les registres en utilisant l'exemple du processeur Intel 8086, qui ne contient que 14 registres à double octet. Dans les processeurs modernes, ils sont beaucoup plus nombreux et de plus grande taille. Cependant, la mémoire du processeur à 14 registres est utilisée comme modèle de base, notamment pour le langage assembleur.

L'OU comprend les registres suivants :

1) registres à usage général (RON) ou universel: AX - (AH, AL), BX - (BH, BL), CX - (CH, CL), DX - (DH, DL) peuvent être utilisés pour stocker temporairement des données, tandis que vous pouvez travailler avec chaque registre comme un entier, et vous pouvez séparément, avec chaque moitié; mais chacun des RON peut être utilisé comme un RON spécial lors de l'exécution de certaines commandes spécifiques ;

2) registres de décalage: SP, BP, SI, DI sont indivisibles et sont destinés à mémoriser les adresses relatives des cellules mémoire au sein des segments (décalages depuis le début des segments) ;

2.1) SP (Empiler Aiguille) - décalage du haut de la pile ;

2.2) PA (Base Aiguille) - décalage de l'adresse de départ du champ mémoire directement alloué pour la pile ;

2.3) SI (La source Indice) , DI (Destination Indice) sont destinés à stocker les adresses de l'index de la source et de la destination des données lors d'opérations sur des chaînes et similaires.

Mot d'état du processeur (PSW – Processeur État Mot) ou inscrivez-vous drapeaux- a une taille de 2 octets et contient des signes ou des drapeaux à un bit. Il y a 9 drapeaux dans le registre : 6 d'entre eux conditionnel ou statut, reflètent les résultats des opérations effectuées par le système d'exploitation, les 3– directeurs généraux, déterminez le mode d'exécution du programme.

1) Indicateurs d'état.

1.1) FC (Transporter Drapeau) - porter le drapeau. Il est mis à 1 si un « report » du bit de poids fort se produit lors de l'exécution d'opérations arithmétiques et de certaines opérations de décalage.

1.2) PF (Drapeau de parité)- drapeau de parité. Vérifie les 8 bits les moins significatifs des résultats sur les données. Un nombre pair de uns fait que ce drapeau est mis à 1, un nombre impair à 0.

1.3) UN F (Auxiliaire Transporter Drapeau) - drapeau de retenue logique en arithmétique binaire-décimale. Mis à 1 si l'opération arithmétique entraîne le transfert ou l'emprunt du quatrième bit à la droite de l'opérande à un octet. Utilisé pour les opérations arithmétiques sur les codes BCD et ASCII.

1.4) ZF (Zéro Drapeau) - drapeau zéro. Mis à 1 si le résultat de l'opération est 0, sinon ZF est mis à zéro.

1.5) SF (Drapeau de signe)- signer le drapeau. Mis à 1 si le résultat de l'opération arithmétique est négatif, à 0 si le résultat est positif.

1.6) DE (Débordement Drapeau) - indicateur de débordement. Défini sur un en cas de débordement arithmétique lorsque le résultat est hors de la grille de bits.

2) Drapeaux de contrôle.

2.1) TF (Piéger Drapeau) - indicateur de trace. Un seul état de ce drapeau met le processeur en mode d'exécution de programme pas à pas.

2.2) SI (indicateur d'interruption)- indicateur d'interruption. Lorsque ce drapeau est à zéro, les interruptions sont désactivées, et lorsqu'il est unique, elles sont activées (le mécanisme d'interruption sera discuté dans le prochain cours).

2.3) DF (Direction Drapeau) - drapeau de direction. Utilisé dans les opérations de chaîne pour spécifier la direction du traitement des données ; lorsque l'état est unique, les lignes sont traitées "de droite à gauche", lorsque l'état est zéro - "de gauche à droite".

L'emplacement des drapeaux dans le registre PSW est illustré à la figure 4.2. Les bits gratuits sont réservés pour une utilisation future.

Figure 4.2 - Disposition des drapeaux dans le registre PSW

Principes architecturaux de l'organisation des processeurs RISC.

Comme indiqué dans / 2, 14, 15 /, la liste des commandes d'un microprocesseur moderne peut contenir un assez grand nombre de commandes. Cependant, tous ne sont pas utilisés aussi souvent et régulièrement. Cette propriété du jeu d'instructions était une condition préalable au développement de processeurs à architecture RISC. L'idée principale était de réduire la liste des commandes utilisées et, par conséquent, de simplifier l'unité de contrôle du processeur et d'organiser une exécution plus rapide des commandes restantes au détriment des ressources cristal libérées dans ce cas.

Les premiers processeurs avec un jeu d'instructions réduit ont été implémentés au début des années 80 du 20ème siècle / 2 / :

1) En 1980, à l'Université de Californie à Berkeley, sous la direction des professeurs David Patterson et Carlo Sequin, un processeur a été développé, qui a été nommé RISC. Les modèles RISC-I, RISC-II, SOLAR ont été développés.

2) En 1981, à l'Université de Stanford, sous la houlette de John Hennesy, un processeur appelé MIPS (Microprocessor Without Interlocked Pipeline Stages) a été conçu. Plus de détails sur l'essence du pipeline seront examinés dans la prochaine question de la conférence.

Plus tard, les deux modèles avec un jeu d'instructions réduit ont été appelés processeurs RISC. Une caractéristique distinctive de ces processeurs est un grand nombre de RON (environ 256).

Décrivons brièvement les principes de base de l'architecture RISC / 2, 15 /.

1) Même longueur de commande... Cela facilite leur récupération à partir de la mémoire principale. Toutes les instructions sont lues en un cycle d'horloge, ce qui permet de traiter le flux d'instructions en pipeline, c'est-à-dire que la synchronisation du matériel du processeur est effectuée, en tenant compte du transfert séquentiel de contrôle d'une unité matérielle à une autre. Dans les processeurs RISC modernes, la longueur des instructions est de 32 bits.

2) Ensemble réduit d'actions sur les opérandes situés en mémoire... Des méthodes simples d'adressage de la mémoire permettent un accès rapide aux opérandes en mémoire. Le traitement des données mis en œuvre lors de l'exécution des commandes RISC n'est jamais associé à des opérations de lecture (écriture) en mémoire (contrairement à de nombreuses commandes CISC). L'échange d'opérandes entre la mémoire et les registres est effectué par des instructions spéciales LOAD et STORE. Le grand nombre de registres de blocs RON permet de réduire le nombre d'accès mémoire.

3) Effectuer toutes les opérations de calcul sur les données situées uniquement dans le RON. Comme il existe de nombreux registres, toutes les variables scalaires et même les petits tableaux de variables sont le plus souvent situés dans des registres, ce qui permet d'accélérer le traitement des données. L'utilisation de commandes simples facilite leur acheminement. En moyenne, les commandes RISC sont exécutées en un cycle d'horloge.

4) Schémas de contrôle relativement simples... Une diminution de la liste des commandes, l'utilisation de commandes ne mettant en œuvre que des opérations simples, et l'exclusion des accès mémoire dans les commandes de traitement de données ont permis de réduire la consommation de ressources cristal pour le contrôle. Grâce à cela, une grande surface de la matrice est allouée pour accueillir des périphériques pouvant augmenter les performances globales du processeur : pipelines supplémentaires, cache accru du 1er niveau, plus de RON.

Il est important de noter qu'avec la même technologie de production, les processeurs RISC ont des fréquences de fonctionnement plus élevées par rapport aux processeurs CISC, ce qui est un avantage important des processeurs RISC.

Selon / 15 /, les unités matérielles suivantes peuvent être distinguées dans l'architecture des processeurs RISC, qui forment les étages du pipeline :

1) Bloc de chargement des instructions comprend les composants suivants : un bloc pour extraire des instructions de la mémoire, un registre d'instructions où l'instruction est placée après l'extraction, et un bloc pour décoder les instructions. Cette étape est appelée étape de récupération des instructions.

2) RON avec les unités de contrôle de registre forment la deuxième étape du pipeline, qui est responsable de la lecture des opérandes d'instruction. Les opérandes peuvent être stockés dans la commande elle-même ou dans l'un des RON. Cette étape est appelée étape d'échantillonnage de l'opérande.

3) ALU et, si une batterie est implémentée dans cette architecture, avec la logique de contrôle, qui, à partir du contenu du registre d'instructions, détermine le type de micro-opération à effectuer. Lors de l'exécution d'opérations de transitions conditionnelles et inconditionnelles, la source de données peut également être un compteur de commandes. Cette étape est appelée étape exécutive du convoyeur.

4) Ensemble de RON et Logic Logic forment une étape de stockage de données. Ici, les résultats de l'exécution de la commande sont écrits dans le RON ou la mémoire principale.

Les processeurs RISC incluent les microprocesseurs MIPS R4000, R8000, R100000 de MIPS Technologies Inc., UltraSPARC I, UltraSPARC II, UltraSPARC III de Sun, PowerPC d'IBM-Motorola, Alpha AXP de DEC, PA-RISC de Hewlett Packard, les microcontrôleurs de Microchip .. .

Malgré les avantages évidents, les processeurs RISC "sous leur forme pure" ne sont pas largement utilisés sur le marché des ordinateurs personnels, la plupart d'entre eux sont utilisés comme unités centrales de traitement des postes de travail. Cependant, la plupart des processeurs CISC modernes, par exemple Pentium, utilisent les réalisations des architectures RISC, en particulier les cœurs RISC pour effectuer des opérations de calcul.

Les modèles de processeurs RISC se développent et s'améliorent activement. À l'heure actuelle, des produits commercialement importants sont mis en œuvre sur leur base : les systèmes SPARC et MIPS.

Des informations plus complètes sur les processeurs RISC, les caractéristiques de leur architecture et leur fonctionnement peuvent être trouvées dans / 2 /, la littérature spéciale et les sources ouvertes sur Internet.

Moyens architecturaux pour améliorer les performances du processeur. Traitement des informations des convoyeurs.

La performance est l'une des caractéristiques les plus importantes d'un processeur. Selon / 2 /, dans le cas général, il est déterminé par la quantité de travail de calcul effectué par unité de temps. Les facteurs les plus importants affectant les performances comprennent la vitesse d'horloge, le nombre d'instructions du programme et le temps d'exécution moyen d'une seule instruction. Pour une évaluation simplifiée des performances du processeur, une métrique est souvent utilisée qui indique le nombre d'instructions exécutées par seconde. Il est défini comme le quotient de la division de la fréquence d'horloge par le temps d'exécution moyen d'une instruction individuelle par le processeur et est mesuré en MIPS (Meg Insruction Per Second) pour les tâches entières et en MFLOPS (Meg Floating Point Operations Per Second) pour la virgule flottante. calculs. Dans ce cas, les estimations de l'indicateur qui détermine le nombre d'instructions exécutées par seconde sont effectuées pour des opérations avec des opérandes de registre, sans être liées à la vitesse de la mémoire principale. Cependant, ce chiffre ne prend pas en compte les caractéristiques architecturales des processeurs spécifiques. Par conséquent, pour les caractéristiques comparatives de divers processeurs, des estimations de performances relatives sont utilisées, pour obtenir quels programmes de test spéciaux sont utilisés.

Conformément à / 2 /, une augmentation des performances des processeurs est obtenue dans la plupart des cas grâce à l'utilisation de solutions technologiques et architecturales spéciales. Les approches technologiques (amélioration des technologies de production de propriété intellectuelle, augmentation du degré d'intégration) ont été abordées précédemment, dans le deuxième chapitre. Par conséquent, attardons-nous plus en détail sur les méthodes architecturales permettant d'augmenter les performances des processeurs. L'amélioration de l'architecture des processeurs, permettant d'augmenter ses performances, est actuellement associée tout d'abord au développement de moyens de traitement parallèle des données. On distingue ici les domaines suivants :

1) Une augmentation du parallélisme "naturel" - une augmentation du nombre de bits de traitement et de transmission de données (le nombre de bits des processeurs est passé de 4 à 32 et 64 bits).

2) Traitement des données du convoyeur (multiphase) - le processus de calcul est divisé en plusieurs phases, chacune utilisant ses propres moyens et un tampon pour stocker le résultat (étape du convoyeur).

3) Traitement de données multi-éléments - traitement de données parallèle dans plusieurs unités d'exploitation (OU) du processeur.

Les méthodes de traitement parallèle peuvent être combinées. Par exemple, dans un processeur, vous pouvez organiser plusieurs unités opérationnelles, chacune utilisant le pipeline.

Examinons plus en détail les deux dernières directions.

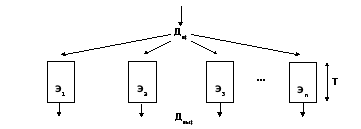

À multiphase traitement, comme le montre la figure 4.3, le processus de traitement des données est divisé en plusieurs étapes (phases), exécutées séquentiellement.

Figure 4.3 - Traitement des données en plusieurs phases

Il existe des tampons entre les phases pour stocker les résultats intermédiaires. Après avoir terminé la première phase, le résultat est stocké dans la mémoire tampon et le traitement de la deuxième phase commence. Les coureurs de la première phase sont libérés et le prochain bloc de données arrive. Si la durée des phases de traitement est la même et est T/ m, alors avec cette méthode, les performances du système augmenteront de m une fois que. Cette méthode correspond au pipeline.

Considérons l'organisation du pipeline au niveau de l'exécution de l'instruction machine / 2 /. Chaque bloc de la chaîne pipeline n'exécute qu'une seule étape d'exécution de la commande. Le traitement complet d'une commande prend plusieurs cycles d'horloge.

Étapes typiques de l'exécution d'une instruction : 1) récupérer l'instruction IF (Instruction Fetch), 2) décoder l'instruction ID (Instruction Decode), 3) lire les opérandes RD (Read Memory), 4) exécuter l'opération EX spécifiée dans l'instruction ( Exécuter), 5) écrire le résultat WB (Write Back). Au cours de l'exécution, la commande se déplace le long du pipeline, libérant l'étape suivante pour la commande suivante. Le contenu des tampons, qui sont utilisés pour stocker les informations transmises le long des étapes du pipeline, est mis à jour à chaque cycle à la fin de l'étape d'exécution de la commande suivante. Les tampons intermédiaires assurent un fonctionnement parallèle indépendant des blocs de la chaîne pipeline : tandis que le bloc suivant commence à exécuter la prochaine étape de commande, le bloc précédent peut commencer à traiter la commande suivante, comme illustré à la Figure 4.4.

|

Cycles du processeur |

||||||||||

|

Commander je | ||||||||||

|

Commander je + 1 | ||||||||||

|

Commander je + 2 | ||||||||||

|

Commander je + 3 | ||||||||||

|

Commander je + 4 | ||||||||||

|

Commander je + 5 | ||||||||||

Figure 4.4 - Traitement des commandes de pipeline

Il convient de noter que le traitement d'instructions pipeline ne réduit pas le temps d'exécution d'une instruction individuelle, qui dans un processeur pipeline reste le même que dans un processeur non pipeline conventionnel. Cependant, du fait que pendant le traitement en pipeline, la majeure partie du processus de calcul est en mode d'exécution simultanée de commandes, la vitesse d'émission des résultats des commandes exécutées séquentiellement augmente proportionnellement au nombre d'étages du pipeline. La durée de l'exécution des différentes étapes de l'exécution de la commande dépend généralement du type de commande et de l'emplacement des opérandes. Le traitement des commandes du pipeline est plus efficace lorsque la durée de toutes les phases d'exécution des commandes est approximativement la même. Malheureusement, il n'est pas toujours possible d'assurer le fonctionnement continu du convoyeur en raison de divers conflits : sur les ressources, selon les données, sur la gestion. Plus de détails sur les conflits - dans / 2, 7 /.

Un processeur dans lequel le processus d'exécution d'une commande est divisé en 5 à 6 étapes est appelé processeur conventionnel. processeur en pipeline... Si vous augmentez le nombre d'étages de convoyeur, chaque étage individuel fera moins de travail et, par conséquent, contiendra moins de logique matérielle. En raison des délais de propagation du signal plus courts dans chaque étage séparé du pipeline, une augmentation de la fréquence de fonctionnement et une augmentation correspondante des performances du processeur sont obtenues. Un processeur avec un pipeline nettement plus profond que 5-6 étapes est appelé super convoyeur... Par exemple, le Pentium II contient 12 étapes, l'UltraSPARC III en a 14 et le Pentium 4 en a 20.

multi-élément

T et le système utilise m T/ m

UNE = B + C; ré = E + F.

superscalairescalairescalaire

Moyens architecturaux pour améliorer les performances du processeur. Traitement de l'information multi-éléments.

Comme le montre l'image 4.5 / 2 /, multi-élément le traitement est effectué sur plusieurs amplificateurs de fonctionnement en parallèle. Chaque élément fait son travail, en traitant une partie des données du début à la fin.

Figure 4.5 - Traitement de données parallèle multi-éléments

Si le temps d'exécution des travaux sur un élément distinct est T et le système utilise méléments, alors avec une certaine idéalisation, on peut s'attendre à ce que le temps moyen pour un tel travail soit T/ m(en fait - moins). Dans les processeurs modernes, ce type de traitement est associé au concept d'architecture superscalaire.

L'exemple le plus simple de parallélisme de calcul est l'exécution de deux instructions dont les opérandes ne sont pas liés l'un à l'autre :

UNE = B + C; ré = E + F.

Par conséquent, les deux commandes peuvent être exécutées en même temps. Pour effectuer des opérations indépendantes, le processeur comprend un ensemble d'unités arithmétiques, dont chacune est généralement mise en pipeline.

Un processeur contenant plusieurs amplificateurs opérationnels qui permet à plusieurs instructions scalaires d'être exécutées en même temps est appelé superscalaire processeur. L'équipe s'appelle scalaire si ses opérandes d'entrée et le résultat sont des nombres (scalaires). Les processeurs traditionnels à ampli-op sont appelés scalaire... Dans un processeur superscalaire, le traitement des instructions est parallélisé non seulement dans le temps (pipeline), mais aussi dans l'espace (plusieurs pipelines). Les performances d'un tel processeur sont évaluées par la vitesse à laquelle les commandes exécutées sortent de tous ses pipelines.

Actuellement, deux méthodes de traitement superscalaire sont utilisées. La première méthode est basée sur un mécanisme purement matériel pour récupérer des instructions de programme non liées à partir de la mémoire (mémoire cache, tampon de prélecture) et les lancer en parallèle pour exécution. Le matériel du processeur est responsable de l'efficacité du chargement des pipelines parallèles, ce qui est le principal avantage de cette méthode de traitement superscalaire. Dans ce cas, le processus de traduction de programmes pour un processeur superscalaire n'est pas différent de la traduction de programmes pour un processeur scalaire traditionnel. Conformément à ce procédé, il est relativement aisé de mettre en oeuvre des microprocesseurs superscalaires de différentes familles qui sont logiciellement compatibles entre eux. Dans ce cas, il n'y a aucun problème avec l'utilisation de logiciels créés précédemment. Tous les processeurs de la famille Pentium sont implémentés de cette manière.

Dans les processeurs mettant en œuvre la deuxième méthode de traitement superscalaire, le compilateur parallélisateur est chargé de programmer l'exécution parallèle de plusieurs instructions. Tout d'abord, il analyse le programme source afin d'identifier les commandes pouvant être exécutées simultanément. Ensuite, le compilateur regroupe ces commandes dans des packages de commandes - mots de commande longs (VLIW), de plus, le nombre de commandes simples dans la commande VLIW est pris égal au nombre d'unités d'exécution du processeur. Étant donné que tout le travail de préparation à l'exécution des commandes VLIW est effectué par le compilateur, les conflits lors de leur exécution sont exclus. Cette méthode de traitement superscalaire est implémentée dans les processeurs VLIW avec une architecture sperscalaire statique. Malheureusement, ces processeurs nécessitent un logiciel spécial. De plus, les programmes compilés pour une génération de microprocesseurs peuvent ne pas fonctionner efficacement sans recompilation sur les processeurs de la prochaine génération. Cela oblige les développeurs de logiciels à développer des versions modifiées fichiers exécutables de son produit pour différentes générations de processeurs. Les idées de VLIW ont été proposées par des ingénieurs et des scientifiques russes dirigés par le professeur B.A. Babayan dans le développement du super-ordinateur domestique "Elbrus-3" (1990). Actuellement, la technologie VLIW est implémentée dans le processeur Elbrus E2K de la société nationale Elbrus International, les processeurs Crusoe de Transmeta, ainsi que dans la famille de processeurs de signal (pour le traitement du signal numérique) TMS320C60xx de Texas Instruments.

Classification et structure des instructions du processeur.

Fonctionnellement, toutes les commandes du processeur peuvent être réparties dans les groupes suivants :

1) commandes d'envoi de données et d'entrée-sortie ;

2) commandes pour les opérations arithmétiques et logiques au niveau du bit ;

3) commandes de transfert de contrôle.

Commandes de transfert de données assurer l'échange d'informations entre les registres du microprocesseur, ainsi que des échanges externes de données lors du transfert vers le processeur depuis la mémoire ou le dispositif d'entrée et du processeur vers la mémoire ou le dispositif de sortie. Ces commandes indiquent généralement le sens de transmission, la source et/ou la destination des données. Par exemple, en assembleur, les commandes de ce groupe incluent la commande forwarding mov, la commande de démarrage CHARGE, commandes d'écriture sur le port et de lecture depuis le port de soufflage, DANS et DEHORS, respectivement, etc. En outre, cela inclut souvent des commandes pour mettre des données sur la pile. POUSSER et extraire les données de la pile POP.

En nombre instructions arithmétiques et logiques au niveau du bit dans la plupart des cas, les commandes incluent les opérations arithmétiques les plus simples, par exemple, ADD (ajouter), SUB (soustraire) et les opérations logiques, par exemple, AND ("AND"), OR ("OR"), etc. Les commandes arithmétiques incluent également les commandes de décalage arithmétique et logique, et les commandes d'opérations logiques incluent les commandes COMPARE (soustraction non destructive). Le nombre de commandes de ce groupe peut comprendre des commandes pour des opérations arithmétiques complexes : multiplication, division (non disponible dans tous les processeurs), instructions de traitement de données en virgule flottante, commandes de traitement multimédia.

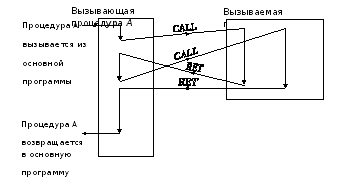

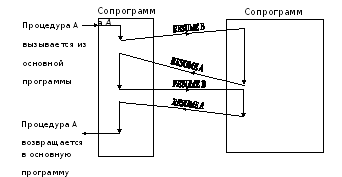

Commandes de transfert de contrôle permettent de modifier la séquence d'exécution des commandes en présence de branches de programme : instructions de saut conditionnelles et inconditionnelles (JMP), appel de sous-programmes (CALL) et sortie de ceux-ci (RETURN). Les instructions de branchement conditionnel mettent en œuvre des transferts de contrôle en fonction de la valeur des drapeaux dans le registre PSW. Avec leur aide, le processeur est l'une des branches possibles de la poursuite du programme. Typiquement, un système de commande a plusieurs commandes de branchement conditionnel.

Dans les processeurs modernes, les systèmes de commande, ainsi que les commandes traditionnelles énumérées ci-dessus, contiennent des groupes de commandes qui étendent les fonctionnalités du microprocesseur pour le traitement des informations, le contrôle de son fonctionnement et la mise en œuvre d'un mode de fonctionnement multitâche sécurisé.

Les systèmes d'instructions de processeurs spécifiques peuvent inclure des instructions qui ne correspondent pas à la classification proposée. De telles commandes ne reflètent pas les principes généraux des programmes de construction et sont considérées comme supplémentaires.

L'exécution d'une commande (opération machine) est divisée en étapes plus petites - des micro-opérations (micro-commandes), au cours desquelles certaines actions élémentaires sont effectuées. La composition spécifique des micro-opérations est déterminée par le système de commande et la structure logique de l'ordinateur. Une séquence de micro-instructions qui implémentent une opération donnée (commande) forme le microprogramme d'opération. L'intervalle de temps pendant lequel une ou plusieurs micro-opérations sont exécutées simultanément est appelé cycle machine. Les limites d'horloge sont définies par les signaux d'horloge, qui sont générés par le générateur de signaux d'horloge.

En général, une commande de microprocesseur contient deux parties : opérationnelle et adresse. Conformément à / 1 /, l'accord sur la répartition des bits entre ces parties de la commande et sur le mode de codage des informations détermine la structure (format) de la commande. La partie opérationnelle de la commande contient un code d'opération qui fournit le codage des opérations (où m- le nombre de bits binaires alloués à la partie opérationnelle de la commande) et détermine quels appareils seront impliqués dans le processeur ou en dehors de celui-ci. V k-bit address partie de la commande contient des informations sur les adresses des opérandes impliqués dans l'opération. En général, la partie adresse de la commande doit contenir quatre champs d'adresse UNE1 , UNE2 , UNE3 , UNE4 ... Ils sont destinés à fixer les adresses des opérandes (A1, A2), l'adresse du résultat (A3) et l'adresse de l'instruction suivante (A4). Comme adresses A1,..., A3, les adresses des cellules RAM et les adresses des registres mémoire du microprocesseur peuvent être utilisées, comme adresse A4, uniquement les adresses des cellules RAM. Lors de l'utilisation de l'ensemble complet d'adresses, le format de commande est lourd. Il a été noté que toutes les opérations ne nécessitent pas l'ensemble complet des adresses A1-A4. Selon le nombre d'adresses spécifié, les commandes sont subdivisées en 0-adresse (non adressé), 1-adresse, 2 adresses, 3-adresse et 4 adresses.

Dans presque tous les microprocesseurs, l'adresse A4 est exclue. Cela est dû au fait que la plupart des instructions appartiennent à des sections linéaires d'algorithmes, et de telles instructions peuvent être placées dans des cellules de mémoire avec des adresses séquentiellement croissantes. Dans ce cas, pour obtenir l'adresse de la commande suivante à l'adresse de départ du segment de code, il suffit d'ajouter son offset dans le segment de code, ce qui est pratique à mettre en œuvre à l'aide du pointeur de commande. Cette façon d'adresser les commandes s'appelle Naturel, et les processeurs qui l'implémentent sont appelés processeurs avec une manière naturelle d'adresser les instructions... En cas de violation de l'ordre naturel des commandes (branches, boucles), des commandes de transfert de contrôle spéciales sont utilisées, qui contiennent l'adresse de transition, mais n'utilisent pas les adresses des opérandes. Les processeurs dont le champ d'adresse d'instruction utilise l'adresse A4 sont appelés processeurs avec une manière forcée d'adresser des commandes.

L'utilisation de l'adresse de résultat A3 est également redondante dans de nombreux cas. Ceci est justifié par le fait que le résultat d'opérations arithmétiques et logiques sur deux opérandes peut généralement être placé à la place de l'un des opérandes, qui ne sera probablement pas utilisé à l'avenir. Dans ce cas, dans les commandes à 2 adresses, des chiffres supplémentaires doivent être saisis dans le champ d'adresse, indiquant lequel d'entre eux est la source et qui est le destinataire de l'information. Dans les processeurs à architecture de batterie, le nombre d'adresses dans la partie adresse de l'instruction est réduit à un. Dans ceux-ci, l'un des opérandes situés dans l'accumulateur est implicitement défini par le code de commande et le résultat est placé dans l'accumulateur.

Dans les commandes non adressées, l'opérande est implicitement spécifié. Ces commandes comprennent des commandes de contrôle du processeur (par exemple, démarrer, arrêter, etc.), des instructions pour travailler avec la pile (l'opérande adressé par le pointeur SP est défini implicitement par le code de commande). Les commandes non adressées ont un format extrêmement abrégé, mais elles ne peuvent pas former indépendamment un système de commande complet sur le plan fonctionnel et ne sont utilisées qu'avec celles avec adresse.

Le format des commandes affecte le temps de résolution des problèmes, la consommation de mémoire, la complexité du processeur et dépend de la classe de problèmes à résoudre. En particulier, pour les calculs scientifiques et techniques, dans lesquels un volume important est occupé par des calculs en plusieurs étapes, les commandes à 1 adresse s'avèrent plus efficaces et, lors de l'utilisation d'un processeur de pile, également les commandes sans adresse. Pour les tâches de contrôle où les transferts et les opérations logiques sont une grande partie, les commandes à 2 adresses sont efficaces. Sur la base de ce qui précède, il convient de noter que les commandes sans adresse, à 1 adresse et à 2 adresses sont généralement utilisées dans les processeurs modernes. Les commandes à 3 adresses sont rarement utilisées et les commandes à 4 adresses ne sont pas du tout utilisées.

En raison de la variété des formats d'instructions et de données (nombres, symboles, structures, etc.), ainsi que de leurs emplacements, diverses manières d'adresser des instructions et des opérandes ont été formées, qui seront discutées ci-dessous.

Méthodes d'adressage des données. Direct, direct, indirect, enregistrez les modes d'adressage relatifs.

Les méthodes d'adressage de données définissent les mécanismes de calcul des adresses effectives des opérandes en mémoire et d'accès aux opérandes. Il existe les méthodes d'adressage (modes) / 2, 6 / suivantes :

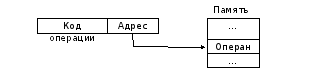

1)Direct- vous permet de définir des valeurs fixes de l'opérande directement dans la partie adresse de la commande, c'est-à-dire que cela fait partie de la commande (Figure 5.1). Ce mode d'adressage est pratique lorsque l'on travaille avec des constantes.

Figure 5.1 - Adressage direct

Exemples : mov ax, 5564h

ajouter al, 1101001100b

N'oubliez pas qu'un opérande immédiat ne peut être spécifié qu'en tant qu'opérande source. L'inconvénient de l'adressage direct est la nécessité d'étendre le format de commande en spécifiant l'opérande lui-même dans le champ d'adresse de commande.

2)Droit- l'adresse de l'opérande est contenue dans le code de commande (Figure 5.2). Il est utilisé lorsque vous travaillez avec des variables et des constantes, dont l'emplacement en mémoire ne change pas pendant l'exécution de la tâche.

Figure 5.2 - Adressage direct

Ainsi, le code instruction indique l'offset de l'opérande en mémoire.

Exemple : segment d_s

supposer ds : d_s, cs : c_s

déplacer hache , mm ; 3154h est envoyé à l'adresse mm

Après avoir exécuté la troisième commande dans le registre hache la valeur sera écrite à l'adresse mm en mémoire, c'est-à-dire le nombre 3154h.

3) S'inscrire- celui-ci est contenu dans le registre défini par la commande, c'est-à-dire que l'adresse du registre est indiquée dans le champ d'adresse de la commande.

Exemples : mov ax, cx

L'adressage de registre est facile à distinguer de tous les autres par le fait que tous les opérandes d'instruction sont des registres. Ces instructions sont les plus compactes et s'exécutent plus rapidement que les autres types d'instructions car il n'y a pas d'accès mémoire.

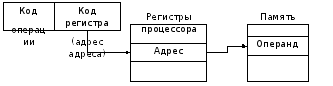

4) Inscription indirecte- est un cas particulier d'adressage indirect, lorsque l'adresse spécifiée dans la commande est un pointeur vers une cellule contenant l'offset de l'opérande en mémoire (Figure 5.3).

En fait, la commande spécifie l'adresse de l'adresse, et le registre de base peut servir de registre d'adresse PA ou registres d'index SI ou DI.

L'adressage indirect est plus efficace que l'adressage direct, puisque seule l'adresse de registre est indiquée dans le champ d'adresse d'instruction, qui est plus court que l'adresse complète de l'opérande en mémoire. Cependant, ce mode d'adressage nécessite un préchargement du registre avec une adresse mémoire indirecte, ce qui consomme du temps supplémentaire.

Exemples : mov hache,

Si dans le registre si contient 10, alors le registre hache placera la valeur à l'offset 10 dans le segment de données.

Figure 5.3 - Adressage indirect

L'adressage indirect est pratique à utiliser lors de la résolution de problèmes, en laissant l'adresse de registre inchangée dans la commande, vous pouvez modifier le contenu de la cellule avec cette adresse.

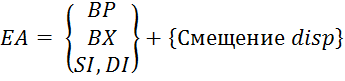

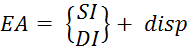

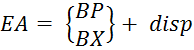

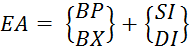

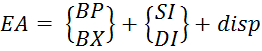

5) Inscrire un parent- est une généralisation des méthodes d'adressage qui permettent le calcul de l'adresse effective ( EA) l'opérande en mémoire comme la somme de la valeur de l'adresse de base et du "offset" disp spécifié dans la commande (Figure 5.4) et (Formule 5.1).

![]()

Figure 5.4 - Formation d'une adresse effective lorsque

adressage relatif

(5.1)

(5.1)